JAJSNZ0D May 2023 – August 2024 UCC21550-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

- 7 詳細説明

- 8 アプリケーションと実装

- 9 電源に関する推奨事項

- 10レイアウト

- 11デバイスおよびドキュメントのサポート

- 12改訂履歴

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- DWK|14

- DW|16

サーマルパッド・メカニカル・データ

発注情報

3 概要

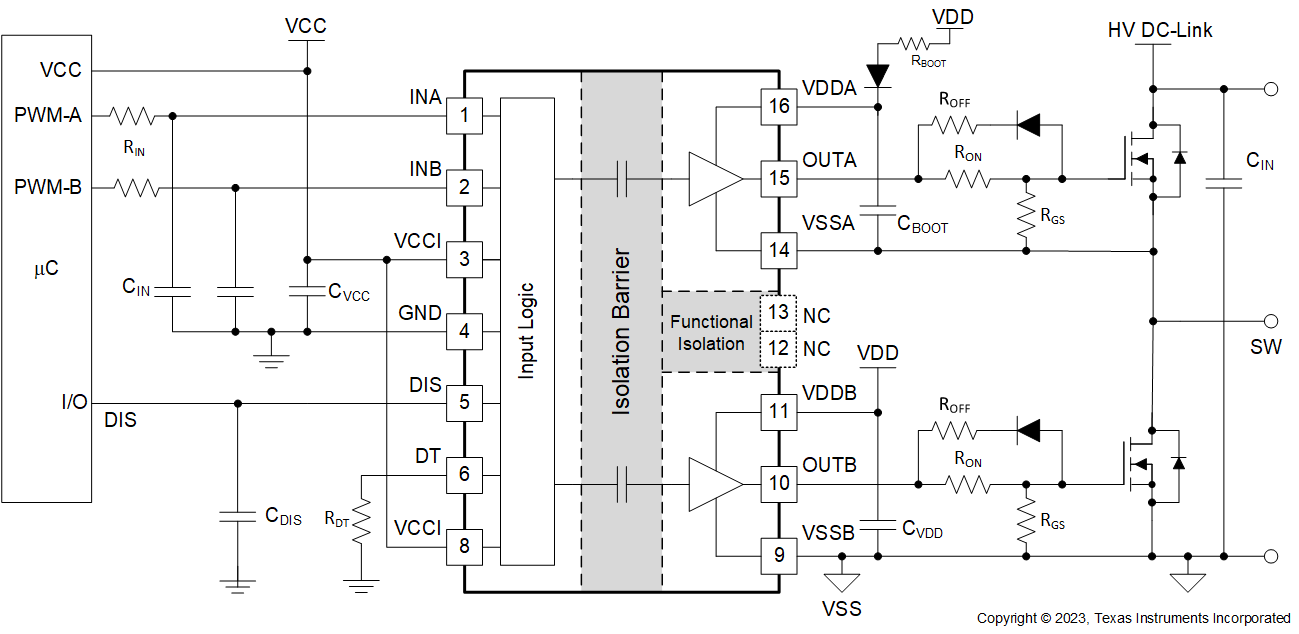

UCC21550-Q1 は、デッド タイムをプログラムでき、広い温度範囲に対応する絶縁型デュアル チャネル ゲート ドライバ ファミリです。ピーク電流はソース 4A、シンク 6A で、パワー MOSFET、SiC、GaN、IGBT トランジスタを駆動するように設計されています。

UCC21550-Q1 は、2 つのローサイド ドライバ、2 つのハイサイド ドライバ、または 1 つのハーフ ブリッジ ドライバとして構成可能です。入力側は、5kVRMS の絶縁バリアによって 2 つの出力ドライバと分離されており、同相過渡耐性 (CMTI) は 125V/ns 以上です。

保護機能には、抵抗によりプログラム可能なデッド タイム、両方の出力を同時にシャットダウンするディセーブル機能、5ns 未満の入力過渡を除去するグリッチ除去フィルタが含まれます。すべての電源が UVLO 機能を備えています。

これらの高度な機能により、UCC21550-Q1 は広範な電力アプリケーションにおいて高効率、高電力密度、および堅牢性を実現します。

製品情報

| 部品番号 | パッケージ (1) | REC.VDD 電源電圧の最小値 |

|---|---|---|

| UCC21550AQDWRQ1 | DW (SOIC、16) | 6.5 V |

| UCC21550BQDWRQ1 | DW (SOIC、16) | 9.2 V |

| UCC21550AQDWKRQ1 | DWK (SOIC、14) | 6.5 V |

| UCC21550BQDWKRQ1 | DWK (SOIC、14) | 9.2 V |

| UCC21550CQDWKRQ1 | DWK (SOIC、14) | 13.5 V |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

代表的なアプリケーション回路図

代表的なアプリケーション回路図