-

ADS42LBx9 14- and 16-Bit, 250-MSPS, Analog-to-Digital Converters

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics: ADS42LB69 (16-Bit)

- 6.6 Electrical Characteristics: ADS42LB49 (14-Bit)

- 6.7 Electrical Characteristics: General

- 6.8 Digital Characteristics

- 6.9 Timing Requirements: General

- 6.10 Timing Requirements: DDR LVDS Mode

- 6.11 Timing Requirements: QDR LVDS Mode

- 6.12 Typical Characteristics: ADS42LB69

- 6.13 Typical Characteristics: ADS42LB49

- 6.14 Typical Characteristics: Common

- 6.15 Typical Characteristics: Contour

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagrams

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1

Description of Serial Interface Registers

- 8.6.1.1 Register 6 (offset = 06h) [reset = 80h]

- 8.6.1.2 Register 7 (offset = 07h) [reset = 00h]

- 8.6.1.3 Register 8 (offset = 08h) [reset = 00h]

- 8.6.1.4 Register B (offset = 0Bh) [reset = 00h]

- 8.6.1.5 Register C (offset = 0Ch) [reset = 00h]

- 8.6.1.6 Register D (offset = 0Dh) [reset = 6Ch]

- 8.6.1.7 Register F (offset = 0Fh) [reset = 00h]

- 8.6.1.8 Register 10 (offset = 10h) [reset = 00h]

- 8.6.1.9 Register 11 (offset = 11h) [reset = 00h]

- 8.6.1.10 Register 12 (offset = 12h) [reset = 00h]

- 8.6.1.11 Register 13 (offset = 13h) [reset = 00h]

- 8.6.1.12 Register 14 (offset = 14h) [reset = 00h]

- 8.6.1.13 Register 15 (offset = 15h) [reset = 00h]

- 8.6.1.14 Register 16 (offset = 16h) [reset = 00h]

- 8.6.1.15 Register 17 (offset = 17h) [reset = 00h]

- 8.6.1.16 Register 18 (offset = 18h) [reset = 00h]

- 8.6.1.17 Register 1F (offset = 1Fh) [reset = 7Fh]

- 8.6.1.18 Register 20 (offset = 20h) [reset = 00h]

- 8.6.1

Description of Serial Interface Registers

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

ADS42LBx9 14- and 16-Bit, 250-MSPS, Analog-to-Digital Converters

1 Features

- Dual Channel

- 14- and 16-Bit Resolution

- Maximum Clock Rate: 250 MSPS

- Analog Input Buffer with High Impedance Input

- Flexible Input Clock Buffer with

Divide-by-1, -2, and -4 - 2-VPP and 2.5-VPP Differential Full-Scale Input (SPI-Programmable)

- DDR or QDR LVDS Interface

- 64-Pin VQFN Package (9-mm × 9-mm)

- Power Dissipation: 820 mW/ch

- Aperture Jitter: 85 fS

- Internal Dither

- Channel Isolation: 100 dB

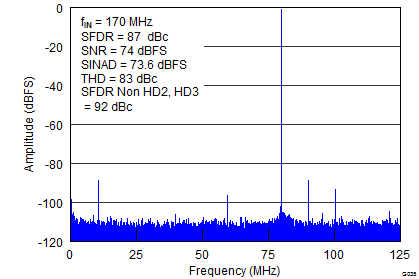

- Performance at fIN = 170 MHz at 2 VPP, –1 dBFS

- SNR: 73.2 dBFS

- SFDR:

- 87 dBc (HD2 and HD3)

- 100 dBc (Non HD2 and HD3)

- Performance at fIN = 170 MHz:

2.5 VPP, –1 dBFS- SNR: 74.9 dBFS

- SFDR:

- 85 dBc (HD2 and HD3)

- 97 dBc (Non HD2 and HD3)

2 Applications

- Communication and Cable Infrastructure

- Multi-Carrier, Multimode Cellular Receivers

- Radar and Smart Antenna Arrays

- Broadband Wireless

- Test and Measurement Systems

- Software-Defined and Diversity Radios

- Microwave and Dual-Channel I/Q Receivers

- Repeaters

- Power Amplifier Linearization

3 Description

The ADS42LB49 and ADS42LB69 are a family of high-linearity, dual-channel, 14- and 16-bit,

250-MSPS, analog-to-digital converters (ADCs) supporting DDR and QDR LVDS output interfaces. The buffered analog input provides uniform input impedance across a wide frequency range while minimizing sample-and-hold glitch energy. A sampling clock divider allows more flexibility for system clock architecture design. The ADS42LBx9 provides excellent spurious-free dynamic range (SFDR) over a large input frequency range with low-power consumption.

Device Information(1)

| PART NUMBER | PACKAGE | INTERFACE OPTION |

|---|---|---|

| ADS42LB49 | VQFN (64) | 14-bit DDR or QDR LVDS |

| 14-bit JESD204B | ||

| ADS42LB69 | VQFN (64) | 16-bit DDR or QDR LVDS |

| 16-bit JESD204B |

- For all available packages, see the orderable addendum at the end of the datasheet.

space

space

Simplified Schematic

4 Revision History

Changes from E Revision (December 2014) to F Revision

- Added Using the ADS42LBx9 In Time-Domain, Low-Frequency Pulse Applications sectionGo

- Added Community Resources section Go

Changes from D Revision (September 2013) to E Revision

- Added ESD Ratings table and Feature Description, Device Functional Modes, Application and Implementation, Power Supply Recommendations, Layout, Device and Documentation Support, and Mechanical, Packaging, and Orderable Information sectionsGo

- Deleted Ordering Information sectionGo

- Merged all Pin Functions tables into one tableGo

- Changed INAP, INAM pin numbers for ADS42LB69 and ADS42LB49 DDR LVDS in pin assignments tableGo

- Added footnote to Table 1 Go

- Added footnote to Table 2 Go

- Changed pin 34 to pin 37 in Figure 79 Go

Changes from C Revision (September 2013) to D Revision

Changes from B Revision (March 2013) to C Revision

- Added pre-RTM changes throughout documentGo

Changes from A Revision (November 2012) to B Revision

- Added pre-RTM changes throughout documentGo

Changes from * Revision (October 2012) to A Revision

- Added pre-RTM changes throughout documentGo

5 Pin Configuration and Functions

Pin Functions

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(3)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| SUPPLIES | ||||||

| AVDD | Analog supply voltage | 1.7 | 1.8 | 1.9 | V | |

| AVDD3V | Analog buffer supply voltage | 3.15 | 3.3 | 3.45 | V | |

| DRVDD | Digital supply voltage | 1.7 | 1.8 | 1.9 | V | |

| ANALOG INPUTS | ||||||

| VID | Differential input voltage range | Default after reset | 2 | VPP | ||

| Register programmable(1) | 2.5 | |||||

| VICR | Input common-mode voltage | VCM ± 0.025 | V | |||

| Maximum analog input frequency with 2.5-VPP input amplitude | 250 | MHz | ||||

| Maximum analog input frequency with 2-VPP input amplitude | 400 | MHz | ||||

| CLOCK INPUT | ||||||

| Input clock sample rate | QDR interface | 30 | 250 | MSPS | ||

| DDR interface | 10 | 250 | ||||

| Input clock amplitude differential (VCLKP – VCLKM) |

Sine wave, ac-coupled | 0.3(2) | 1.5 | VPP | ||

| LVPECL, ac-coupled | 1.6 | |||||

| LVDS, ac-coupled | 0.7 | |||||

| LVCMOS, single-ended, ac-coupled | 1.5 | V | ||||

| Input clock duty cycle | 35% | 50% | 65% | |||

| DIGITAL OUTPUTS | ||||||

| CLOAD | Maximum external load capacitance from each output pin to DRGND | 3.3 | pF | |||

| RLOAD | Single-ended load resistance | +50 | Ω | |||

| TA | Operating free-air temperature | –40 | +85 | °C | ||

6.4 Thermal Information

| THERMAL METRIC(1) | ADS42LBx9 | UNIT | |

|---|---|---|---|

| RGC (VQFN) | |||

| 64 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 22.9 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 7.1 | °C/W |

| RθJB | Junction-to-board thermal resistance | 2.5 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.1 | °C/W |

| ψJB | Junction-to-board characterization parameter | 2.5 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 0.2 | °C/W |

6.5 Electrical Characteristics: ADS42LB69 (16-Bit)

Typical values are at TA = +25°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, 50% clock duty cycle, –1-dBFS differential analog input, and sampling rate = 250 MSPS, unless otherwise noted. Minimum and maximum values are across the full temperature range of TMIN = –40°C to TMAX = +85°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V.6.6 Electrical Characteristics: ADS42LB49 (14-Bit)

Typical values are at TA = +25°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, 50% clock duty cycle, –1-dBFS differential analog input, and sampling rate = 250 MSPS, unless otherwise noted. Minimum and maximum values are across the full temperature range of TMIN = –40°C to TMAX = +85°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V.6.7 Electrical Characteristics: General

Typical values are at +25°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, 50% clock duty cycle, –1-dBFS differential analog input, and sampling rate = 250 MSPS, unless otherwise noted. Minimum and maximum values are across the full temperature range: TMIN = –40°C to TMAX = +85°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ANALOG INPUTS | ||||||

| VID | Differential input voltage range | Default (after reset) | 2 | VPP | ||

| Register programmed(1) | 2.5 | |||||

| Differential input resistance (at 170 MHz) | 1.2 | kΩ | ||||

| Differential input capacitance (at 170 MHz) | 4 | pF | ||||

| Analog input bandwidth | With 50-Ω source impedance, and 50-Ω termination | 900 | MHz | |||

| VCM | Common-mode output voltage | 1.9 | V | |||

| VCM output current capability | 10 | mA | ||||

| DC ACCURACY | ||||||

| Offset error | –20 | 20 | mV | |||

| EGREF | Gain error as a result of internal reference inaccuracy alone | ±2 | %FS | |||

| EGCHAN | Gain error of channel alone | –5 | %FS | |||

| Temperature coefficient of EGCHAN | 0.01 | Δ%/°C | ||||

| POWER SUPPLY | ||||||

| IAVDD | Analog supply current | 141 | 182 | mA | ||

| IAVDD3V | Analog buffer supply current | 302 | 340 | mA | ||

| IDRVDD | Digital and output buffer supply current | External 100-Ω differential termination on LVDS outputs | 219 | 245 | mA | |

| Analog power | 253 | mW | ||||

| Analog buffer power | 996 | mW | ||||

| Power consumption (includes digital blocks and output buffers) | External 100-Ω differential termination on LVDS outputs | 393 | mW | |||

| Total power | 1.64 | 1.85 | W | |||

| Global power-down (both channels) | 160 | mW | ||||

6.8 Digital Characteristics

The dc specifications refer to the condition where the digital outputs are not switching, but are permanently at a valid logic level '0' or '1'. AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, and, unless otherwise noted.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| DIGITAL INPUTS (RESET, SCLK, SDATA, SEN, CTRL1, CTRL2)(1) | |||||||

| VIH | High-level input voltage | All digital inputs support 1.8-V and 3.3-V CMOS logic levels | 1.3 | V | |||

| VIL | Low-level input voltage | 0.4 | V | ||||

| IIH | High-level input current | RESET, SDATA, SCLK, CTRL1, CTRL2(2) | VHIGH = 1.8 V | 10 | µA | ||

| SEN(3) | VHIGH = 1.8 V | 0 | |||||

| IIL | Low-level input current | RESET, SDATA, SCLK, CTRL1, CTRL2 | VLOW = 0 V | 0 | µA | ||

| SEN | VLOW = 0 V | 10 | |||||

| DIGITAL OUTPUTS, CMOS INTERFACE (OVRA, OVRB, SDOUT) | |||||||

| VOH | High-level output voltage | DRVDD – 0.1 | DRVDD | V | |||

| VOL | Low-level output voltage | 0 | 0.1 | V | |||

| DIGITAL OUTPUTS, LVDS INTERFACE | |||||||

| VODH | High-level output differential voltage | With an external 100-Ω termination |

250 | 350 | 500 | mV | |

| VODL | Low-level output differential voltage | With an external 100-Ω termination |

–500 | –350 | –250 | mV | |

| VOCM | Output common-mode voltage | 1.05 | V | ||||

6.9 Timing Requirements: General

Typical values are at +25°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, sampling frequency = 250 MSPS, sine wave input clock, CLOAD = 3.3 pF, and RLOAD = 100 Ω, unless otherwise noted. Minimum and maximum values are across the full temperature range: TMIN = –40°C to TMAX = +85°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.7 V to 1.9 V.| MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| tA | Aperture delay | 0.5 | 0.7 | 1.1 | ns | |

| Aperture delay matching between two channels of the same device | ±70 | ps | ||||

| Variation of aperture delay between two devices at the same temperature and supply voltage | ±150 | ps | ||||

| tJ | Aperture jitter | 85 | fS rms | |||

| Wakeup time | Time to valid data after coming out of STANDBY mode | 50 | 100 | µs | ||

| Time to valid data after coming out of GLOBAL power-down mode (in this mode, both channels power-down) | 250 | 1000 | µs | |||

| ADC latency(3) | Default latency after reset | 14 | Clock cycles | |||

| Normal OVR latency | 14 | Clock cycles | ||||

| Fast OVR latency | 9 | Clock cycles | ||||

| tSU_SYNCIN | Setup time for SYNCIN, referenced to input clock rising edge | 400 | ps | |||

| tH_SYNCIN | Hold time for SYNCIN, referenced to input clock rising edge | 100 | ps | |||

6.10 Timing Requirements: DDR LVDS Mode(1)

Typical values are at +25°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, sampling frequency = 250 MSPS, sine wave input clock, CLOAD = 3.3 pF, and RLOAD = 100 Ω, unless otherwise noted. Minimum and maximum values are across the full temperature range: TMIN = –40°C to TMAX = +85°C, AVDD = 1.8 V, AVDD3V = 3.3 V, and DRVDD = 1.7 V to 1.9 V.| MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| tSU | Data setup time: data valid to zero-crossing of differential output clock (CLKOUTP – CLKOUTM)(2) |

0.62 | 0.82 | ns | ||

| tHO | Data hold time: zero-crossing of differential output clock (CLKOUTP – CLKOUTM) to data becoming invalid(2) | 0.54 | 0.64 | ns | ||

| tPDI | Clock propagation delay: input clock rising edge cross-over to output clock (CLKOUTP – CLKOUTM) rising edge cross-over | 8 | 10.5 | 13 | ns | |

| LVDS bit clock duty cycle: duty cycle of differential clock (CLKOUTP – CLKOUTM) | 52% | |||||

| tFALL, tRISE |

Data fall time, data rise time: rise time measured from –100 mV to +100 mV, 10 MSPS ≤ sampling frequency ≤ 250 MSPS |

0.14 | ns | |||

| tCLKRISE, tCLKFALL |

Output clock rise time, output clock fall time: Rise time measured from –100 mV to +100 mV, 10 MSPS ≤ sampling frequency ≤ 250 MSPS |

0.18 | ns | |||

Table 1. DDR LVDS Timings at Lower Sampling Frequencies(1)

| SAMPLING FREQUENCY (MSPS) | SETUP TIME | HOLD TIME | CLOCK PROPAGATION DELAY |

UNIT | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| tSU | tHO | tPDI | ||||||||

| MIN | TYP | MAX | MIN | TYP | MAX | MIN | TYP | MAX | ||

| 80 | 2.40 | 2.96 | 2.16 | 2.82 | 9 | 11.9 | 15 | ns | ||

| 120 | 1.57 | 1.92 | 1.40 | 1.84 | 8 | 11.1 | 14 | |||

| 160 | 1.17 | 1.40 | 1.02 | 1.36 | 8 | 10.6 | 13 | |||

| 200 | 0.82 | 1.07 | 0.72 | 1.02 | 8 | 10.5 | 13 | |||

| 230 | 0.69 | 0.91 | 0.61 | 0.84 | 8 | 10.5 | 13 | |||

6.11 Timing Requirements: QDR LVDS Mode(4)(1)

Typical values are at +25°C, AVDD = 1.8 V, AVDD3V = 3.3 V, DRVDD = 1.8 V, sampling frequency = 250 MSPS, sine-wave input clock, CLOAD = 3.3 pF(2), and RLOAD = 100 Ω(3), unless otherwise noted. Minimum and maximum values are across the full temperature range of TMIN = –40°C to TMAX = +85°C, AVDD = 1.8 V, AVDD3V = 3.3 V, and DRVDD = 1.7 V to 1.9 V.| MIN | TYP | MAX | UNIT | ||||

|---|---|---|---|---|---|---|---|

| tSU | Data setup time(5)(6): data valid to DxCLKP, DxCLKM zero-crossing | 0.23 | 0.31 | ns | |||

| tH | Data hold time(5)(6): DxCLKP, DxCLKM zero-crossing to data becoming invalid | 0.16 | 0.29 | ns | |||

| LVDS bit clock duty cycle: differential bit clock duty cycle (DxCLKP, DxCLKM) | 50% | ||||||

| tPDI | Clock propagation delay: input clock rising edge cross-over to output frame clock (DxFRAMEP-DxFRAMEM) rising edge cross-over |

7 | 10.1 | 13 | ns | ||

| tRISE, tFALL | Data rise and fall time: rise time measured from –100 mV to +100 mV | 0.18 | ns | ||||

| tCLKRISE, tCLKFALL | Output clock rise and fall time: rise time measured from –100 mV to +100 mV | 0.2 | ns | ||||

Table 2. QDR LVDS Timings at Lower Sampling Frequencies(1)

| SAMPLING FREQUENCY (MSPS) | SETUP TIME | HOLD TIME | CLOCK PROPAGATION DELAY |

UNIT | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| tSU | tHO | tPDI | ||||||||

| MIN | TYP | MAX | MIN | TYP | MAX | MIN | TYP | MAX | ||

| 80 | 1.06 | 1.21 | 0.84 | 1.29 | 6 | 9.3 | 12 | ns | ||

| 120 | 0.63 | 0.77 | 0.66 | 0.88 | 7 | 9.5 | 13 | |||

| 160 | 0.43 | 0.55 | 0.39 | 0.61 | 7 | 9.7 | 13 | |||

| 200 | 0.31 | 0.42 | 0.28 | 0.47 | 7 | 9.8 | 13 | |||

| 230 | 0.24 | 0.34 | 0.17 | 0.36 | 7 | 9.9 | 13 | |||

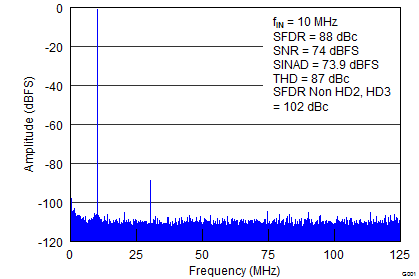

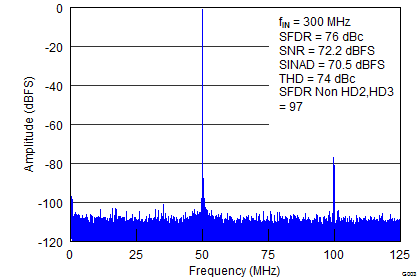

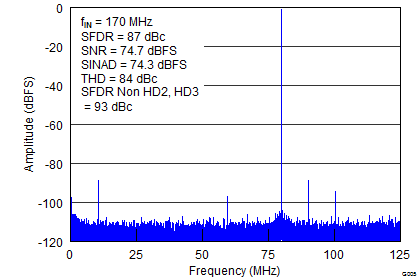

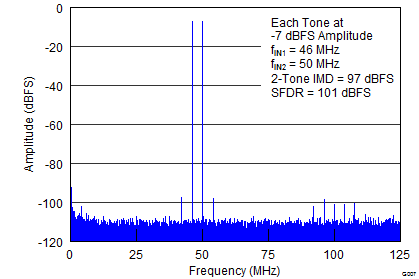

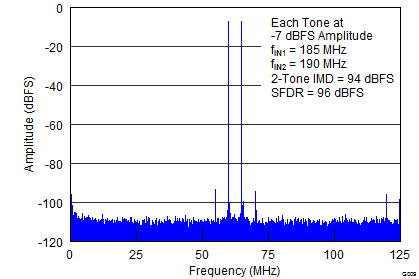

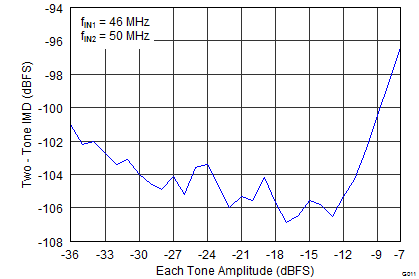

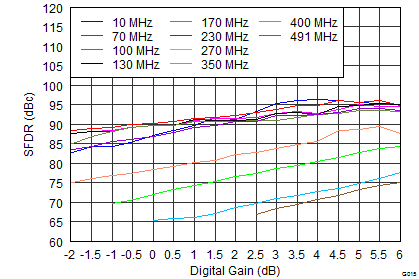

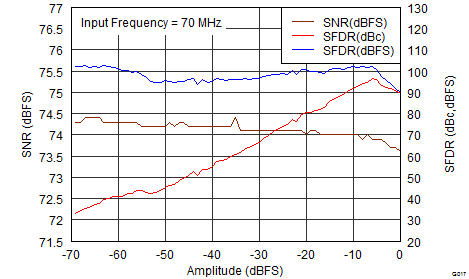

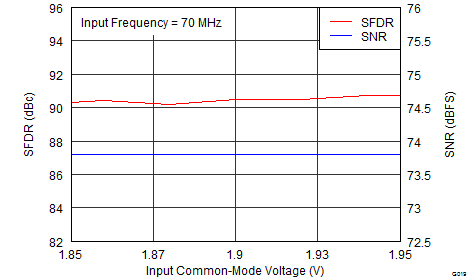

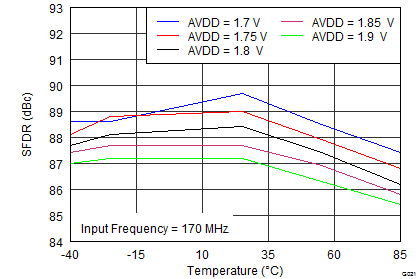

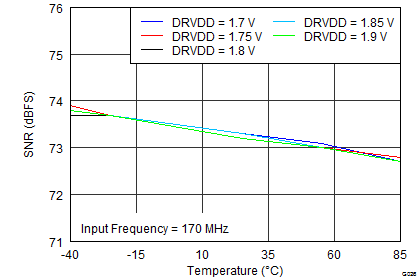

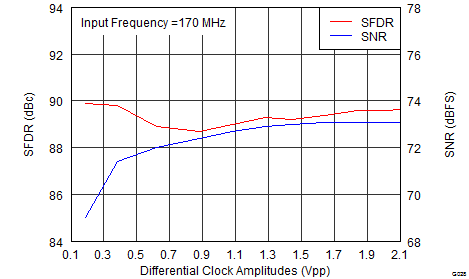

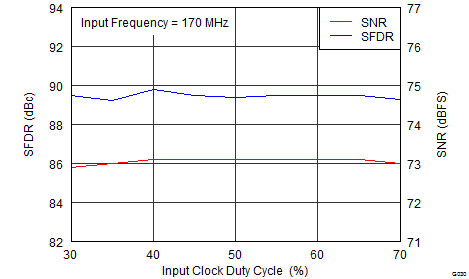

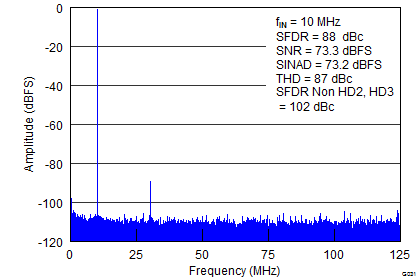

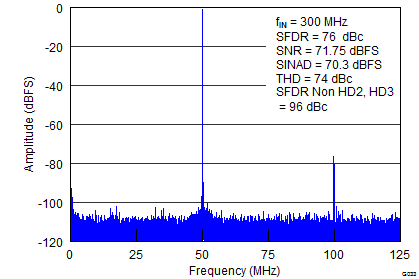

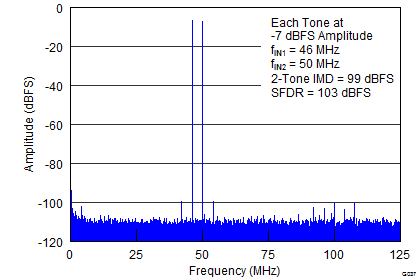

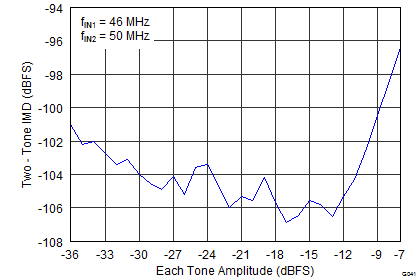

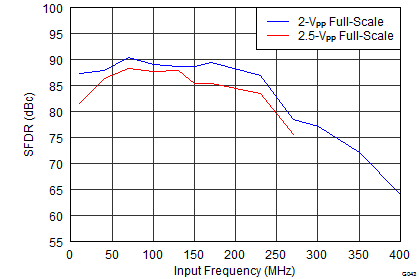

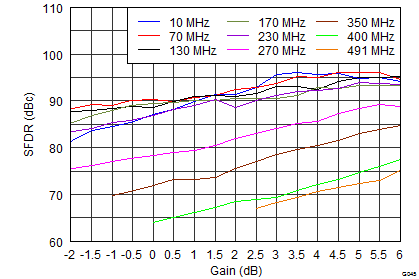

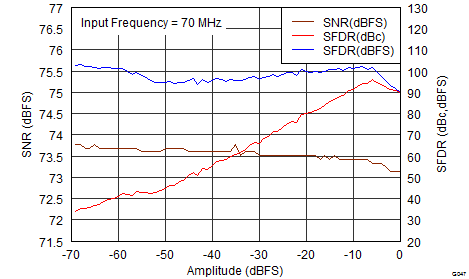

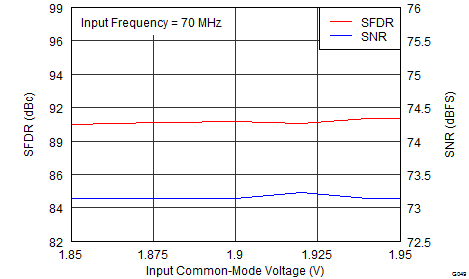

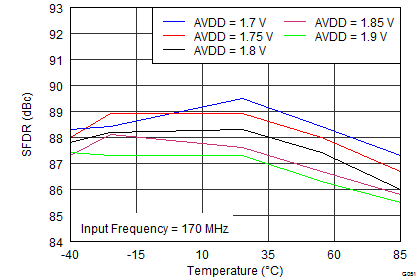

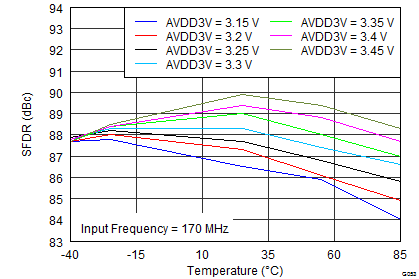

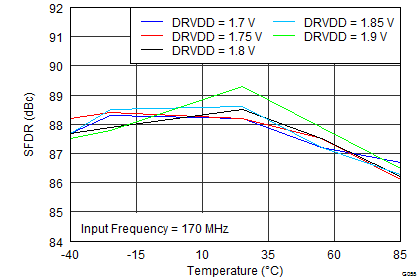

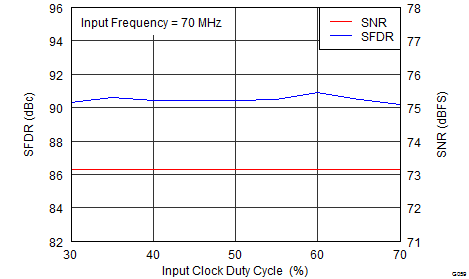

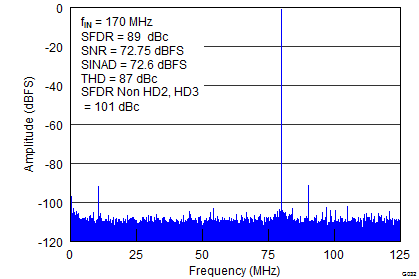

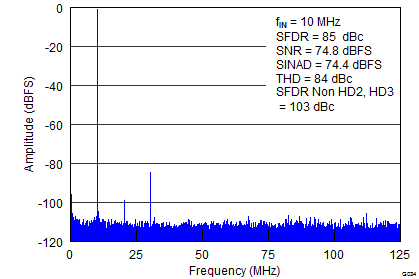

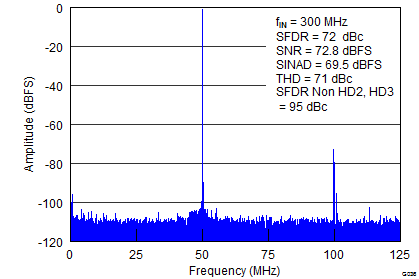

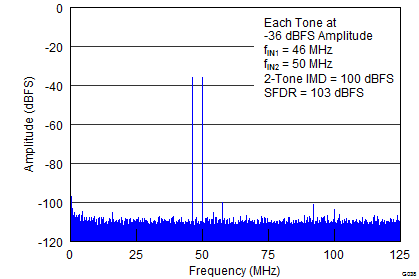

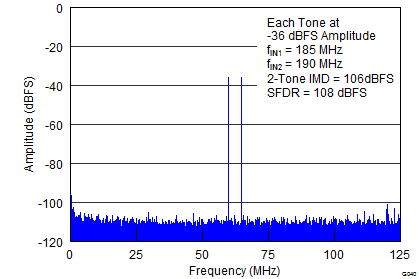

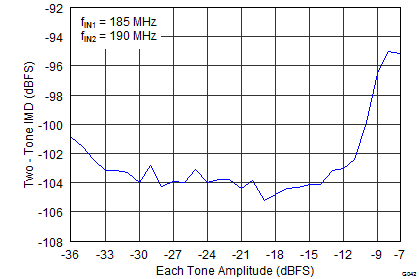

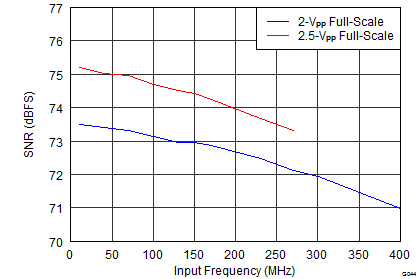

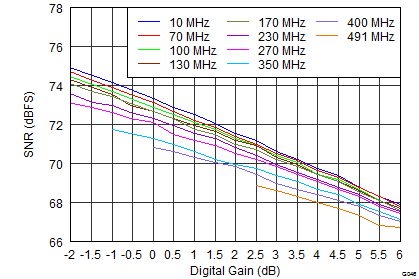

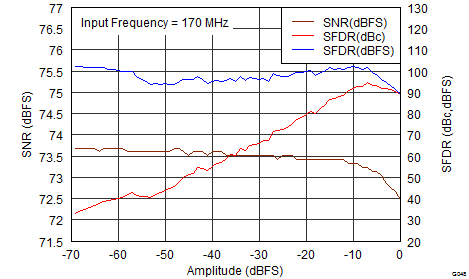

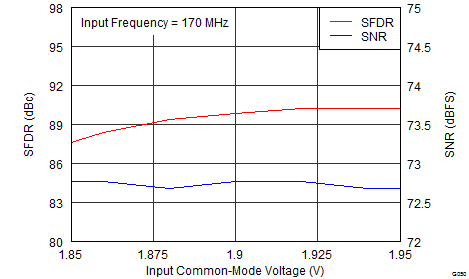

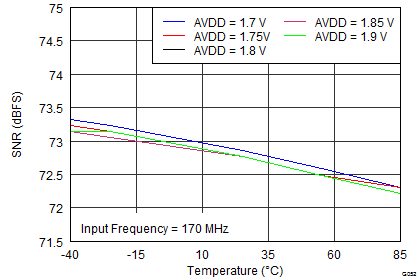

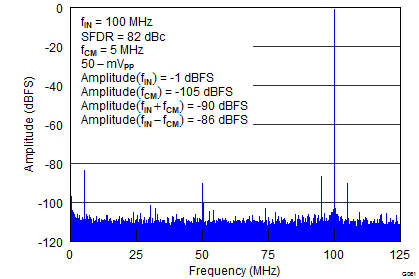

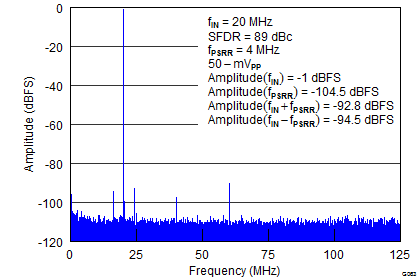

6.12 Typical Characteristics: ADS42LB69

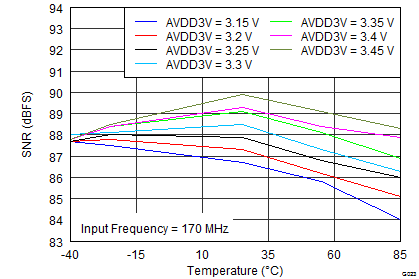

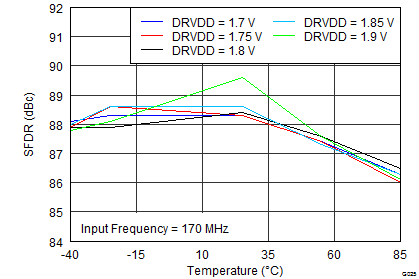

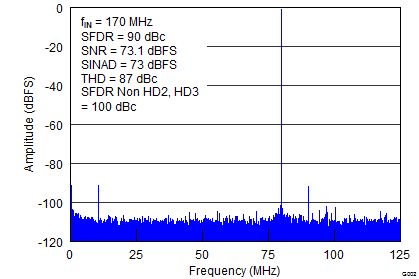

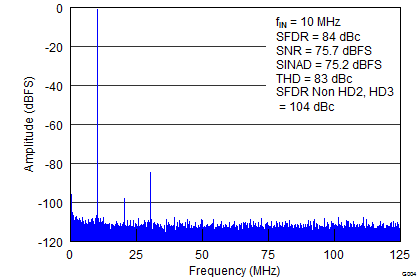

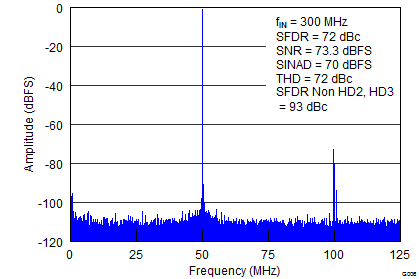

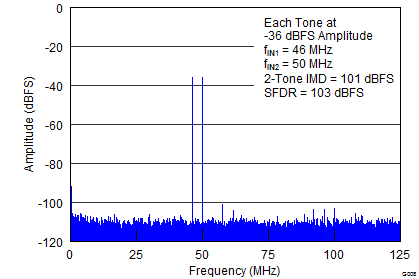

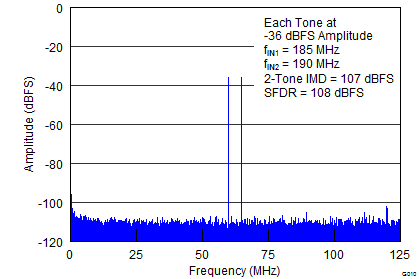

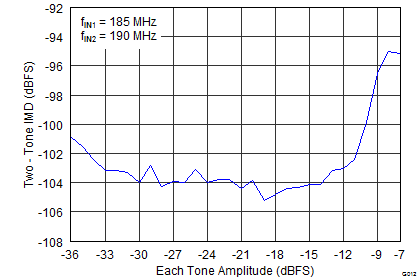

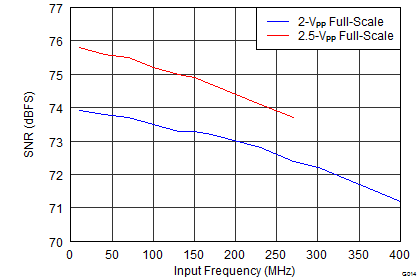

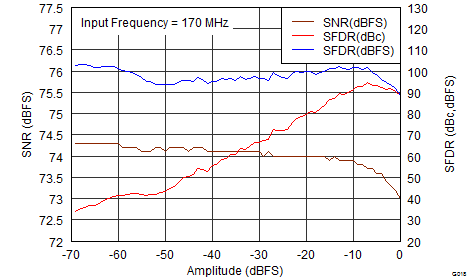

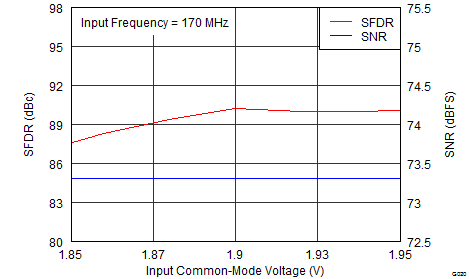

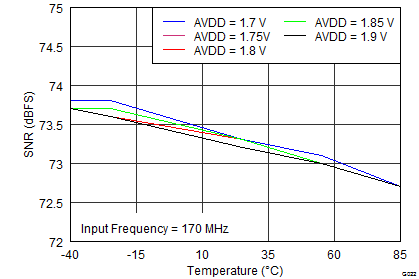

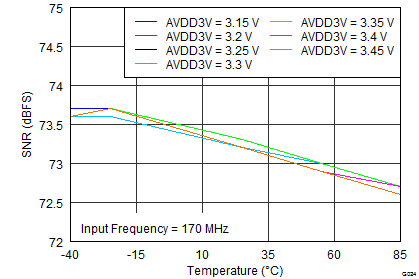

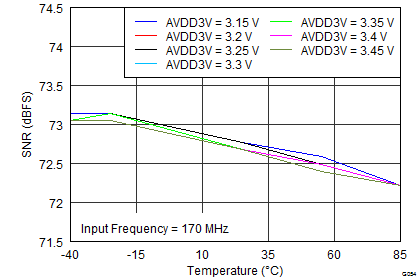

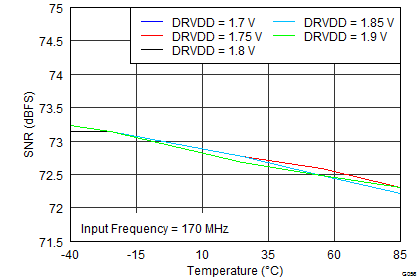

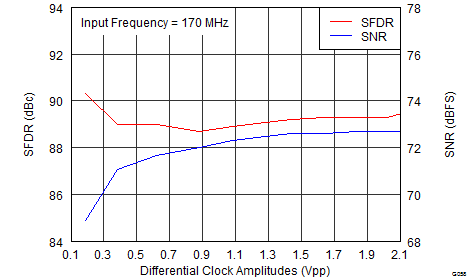

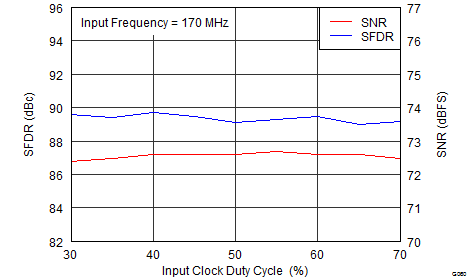

Typical values are at TA = +25°C, full temperature range is TMIN = –40°C to TMAX = +85°C, ADC sampling rate = 250 MSPS, 50% clock duty cycle, QDR interface, AVDD3V = 3.3 V, AVDD = DRVDD = 1.8 V, –1-dBFS differential input, and 32k-point FFT, unless otherwise noted.

(2.5-VPP Full-Scale)

(At –7 dBFS, 46 MHz and 50 MHz)

(At –7 dBFS, 185 MHz and 190 MHz)

(46 MHz and 50 MHz)

(70 MHz)

(70 MHz)

(170 MHz)

(170 MHz)

(70 MHz)

(70 MHz)

(2.5-VPP Full-Scale)

(2.5-VPP Full-Scale)

(At –36 dBFS, 46 MHz and 50 MHz)

(At –36 dBFS, 185 MHz and 190 MHz)

(185 MHz and 190 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

6.13 Typical Characteristics: ADS42LB49

Typical values are at TA = +25°C, full temperature range is TMIN = –40°C to TMAX = +85°C, ADC sampling rate = 250 MSPS, 50% clock duty cycle, AVDD3V = 3.3 V, AVDD = DRVDD = 1.8 V, –1-dBFS differential input, and 32k-point FFT, unless otherwise noted.

(2.5-VPP Full-Scale)

(At –7 dBFS, 46 MHz and 50 MHz)

(At –7 dBFS, 185 MHz and 190 MHz)

(46 MHz and 50 MHz)

(70 MHz)

(70 MHz)

(170 MHz)

(170 MHz)

(70 MHz)

(70 MHz)

(2.5-VPP Full-Scale)

(2.5-VPP Full-Scale)

(At –36 dBFS, 46 MHz and 50 MHz)

(At –36 dBFS, 185 MHz and 190 MHz)

(185 MHz and 190 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

(170 MHz)

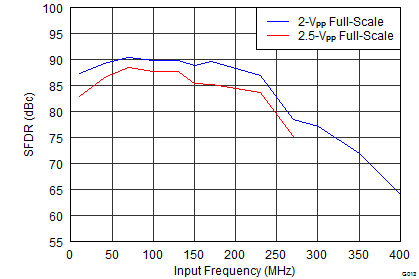

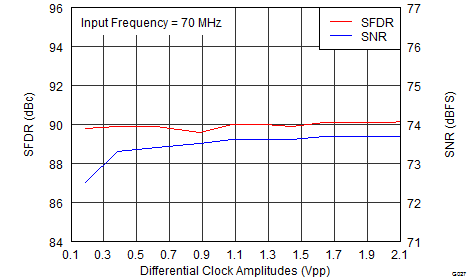

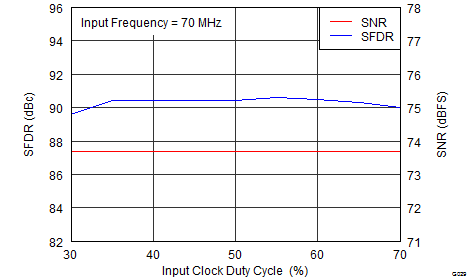

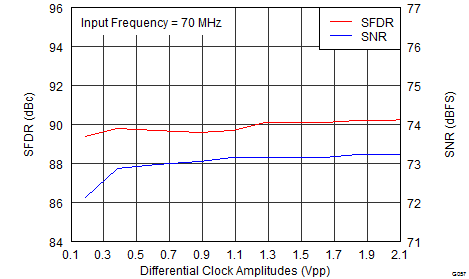

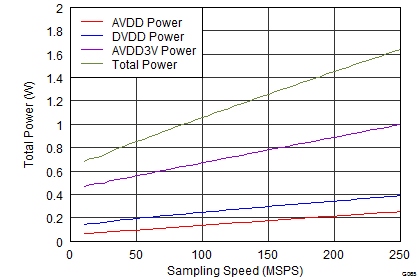

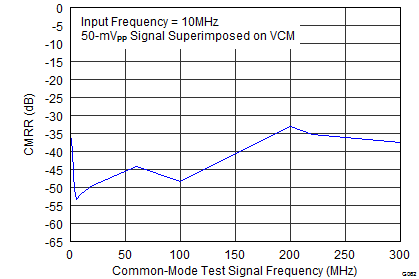

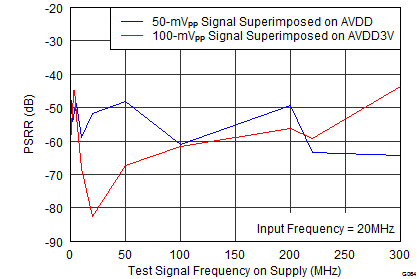

6.14 Typical Characteristics: Common

Typical values are at TA = +25°C, full temperature range is TMIN = –40°C to TMAX = +85°C, ADC sampling rate = 250 MSPS, 50% clock duty cycle, AVDD3V = 3.3 V, AVDD = DRVDD = 1.8 V, –1-dBFS differential input, and 32k-point FFT, unless otherwise noted.

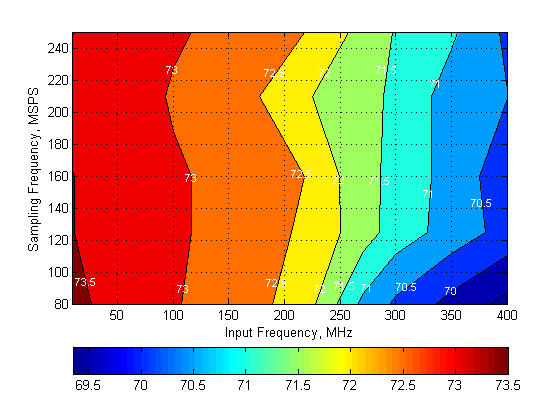

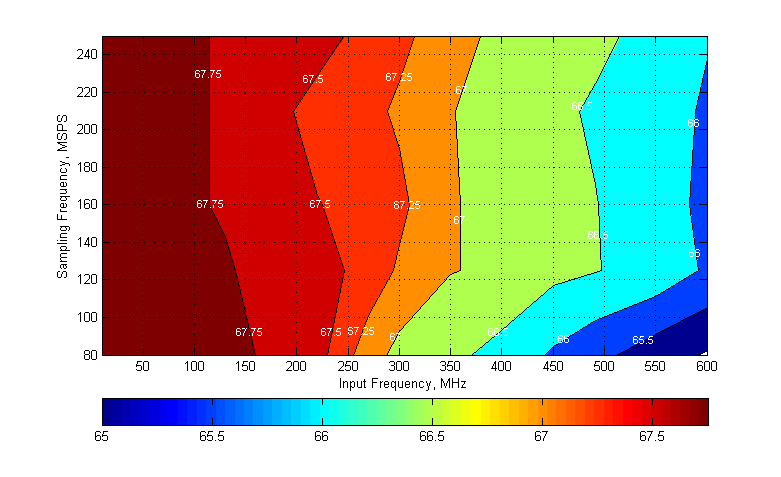

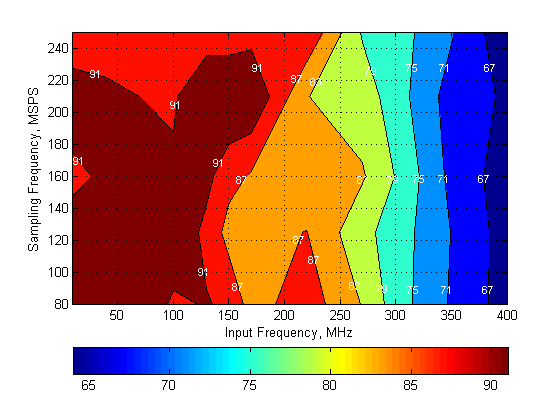

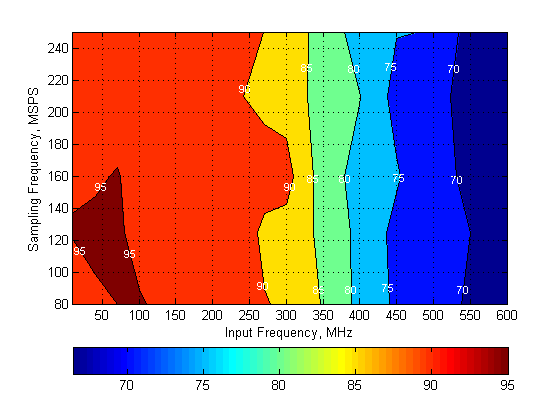

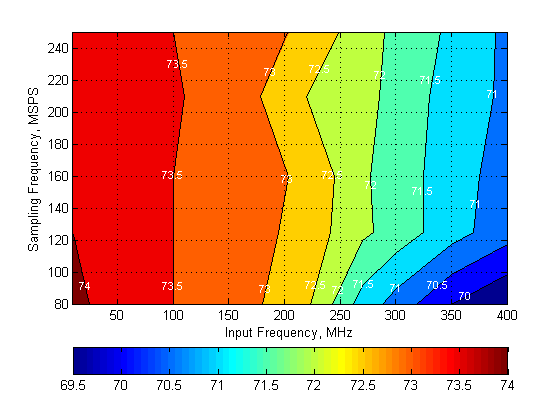

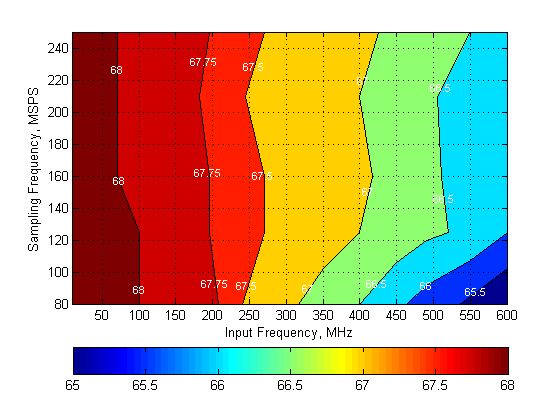

6.15 Typical Characteristics: Contour

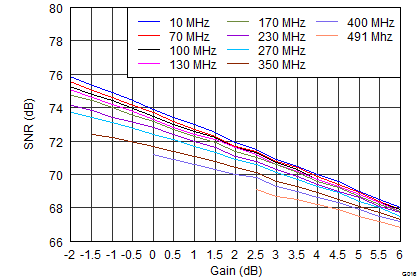

Typical values are at TA = +25°C, full temperature range is TMIN = –40°C to TMAX = +85°C, ADC sampling rate = 250 MSPS, 50% clock duty cycle, AVDD3V = 3.3 V, AVDD = DRVDD = 1.8 V, –1-dBFS differential input, and 65k-point FFT, unless otherwise noted.6.15.1 Spurious-Free Dynamic Range (SFDR): General

6.15.2 Signal-to-Noise Ratio (SNR): ADS42LB69

6.15.3 Signal-to-Noise Ratio (SNR): ADS42LB49