JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

9.2 グランド・レイアウトに関する検討事項

システム・グランドは、ボード上のノイズと EMI の問題に関連する最も重要な領域と基盤です。これらの問題を最小化する最も実用的な方法は、個別のグランド・プレーンを用意することです。

グランド・ノイズとは?

回路 (ドライバなど) から発生する各信号は、グランド・パスを経由してソースに電流を戻します。周波数が高くなるにつれて、またはリレーのように単純で大電流のスイッチングを行う場合でも、接地方式で干渉を発生させるライン・インピーダンスに起因する電圧降下が発生します。リターン・パスは常に最小の抵抗を経由します。DC 信号の場合、最も抵抗性の低いパスになり、高周波信号の場合は、最もインピーダンスの低いパスになります。これは、グランド・プレーンを使用して問題を簡素化する方法を説明し、シグナル・インテグリティを確保するための鍵となります。

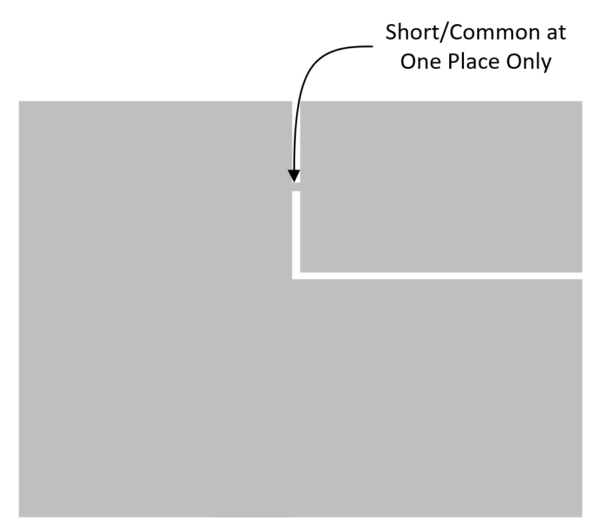

デジタル復帰信号がアナログ復帰 (グランド) 領域内に伝搬することは推奨されません。したがって、設計者はグランド・プレーンを分割して、すべてのデジタル信号復帰ループをグランド領域内に維持する必要があります。この分割は慎重に行う必要があります。多くの設計では、単一 (コモン) の電圧レギュレータを使用して、同じ電圧レベル (3.3V など) のデジタルおよびアナログ電源を生成します。アナログ・レールとデジタル電源レール、およびそれぞれのグランドを互いに絶縁する必要があります。グランドを絶縁するときは、両方のグランドをどこかに短絡する必要があるため、注意してください。図 9-2に、デジタル信号のリターン・パスがアナログ・グランドを通過するループを形成できないことを示します。各設計で、部品の配置などを考慮して一般的なポイントを決定します。グランド・トレースと直列にインダクタ (フェライト・ビーズ) や抵抗 (ゼロ Ω ではない) を追加しないでください。高周波での関連インダクタンスによりインピーダンスが増加し、電圧差が生じます。デジタル・グランドを基準とする信号は、アナログ・グランドまたは他の方向には配線しないでください。

図 9-2 デジタル・グランドとアナログ・グランド、および共通領域

図 9-2 デジタル・グランドとアナログ・グランド、および共通領域