JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

9.1 電源レイアウト

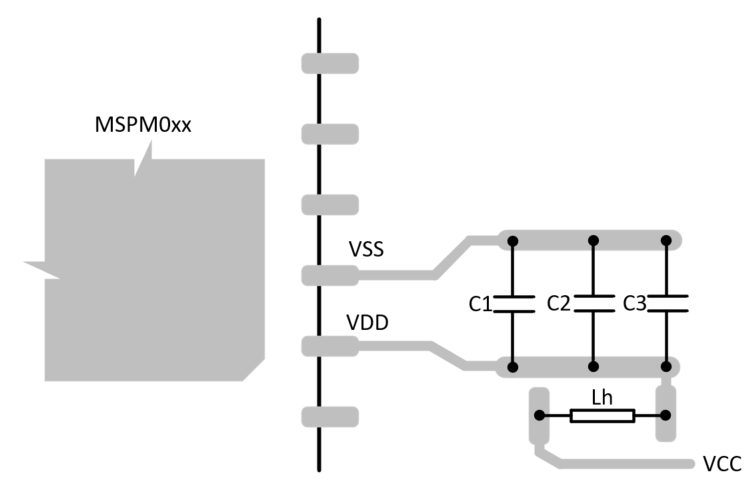

図 9-1に、電源レイアウトの代表的な部品配置と配線を示します。MSPM0G 部品に合わせて適切に変更する必要があります。オプションとして、VCC および MCU VDD ピンと直列にフィルタ・インダクタを接続できます。このインダクタを使用して、DC / DC のスイッチング・ノイズ周波数をフィルタリングします。値については、DC / DC ベンダのデータシートを参照してください。MSPM0G デバイスのデータシートに掲載されている C1/C2/C3 の値とレイアウト。

注:

- 最小の容量は、MCU VDD ピンにできるだけ近い値 (C1 < C2 < C3) に維持します。

- すべてのトレースをビアなしで直接配線します。

図 9-1 推奨される電源レイアウト

図 9-1 推奨される電源レイアウト