JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

7.2 UART と LIN のリソースと設計の検討事項

MSPM0G シリーズ MCU には、ユニバーサル非同期送受信機 (UART) が搭載されています。表 7-4 に示すように、UART0 は LIN、DALI、IrDA、ISO7816 マンチェスター符号化機能をサポートしています。

| UART の特長 | UART0 (拡張) | UART1 (メイン) |

|---|---|---|

| 停止およびスタンバイ・モードでアクティブ | あり | あり |

| 送信 FIFO と受信 FIFO を分離 | あり | あり |

| ハードウェア・フロー制御をサポート | あり | あり |

| 9 ビット構成をサポート | あり | あり |

| LIN モードをサポート | あり | - |

| DALI をサポート | あり | - |

| IrDA をサポート | あり | - |

| ISO7816 スマート・カードをサポート | あり | - |

| マンチェスター符号化をサポート | あり | - |

MSPM0G UART モジュールは、ほぼすべての UART アプリケーションをサポートするため、パワー・ドメイン 1 で最高 10MHz のボー・データをサポートできます。

| パラメータ | テスト条件 | 最小値 | 標準値 | 最大値 | 単位 | |

|---|---|---|---|---|---|---|

| fUART | UART 入力クロック周波数 | パワー・ドメイン 1 の UART | 80 | MHz | ||

| fUART | UART 入力クロック周波数 | パワー・ドメイン 0 の UART | 40 | MHz | ||

| fBITCLK | BITCLK クロック周波数 (MBaud のボー・レートに等しい) | パワー・ドメイン 1 の UART | 10 | MHz | ||

| fBITCLK | BITCLK クロック周波数 (MBaud のボー・レートに等しい) | 5 | MHz | |||

| tSP | 入力フィルタにより抑制されるスパイクのパルス持続時間 | AGFSELx = 0 | 5 | 5.5 | 32 | ns |

| AGFSELx = 1 | 8 | 15 | 55 | ns | ||

| AGFSELx = 2 | 18 | 38 | 115 | ns | ||

| AGFSELx = 3 | 30 | 74 | 165 | ns | ||

ローカル相互接続ネットワーク (LIN) は一般的に使用される低速ネットワーク・インターフェイスで、複数のリモート・レスポンダ・ノードと通信するコマンダ・ノードで構成されています。通信に必要なのは 1 本のワイヤのみであり、一般的に車両の配線ハーネスに含まれています。

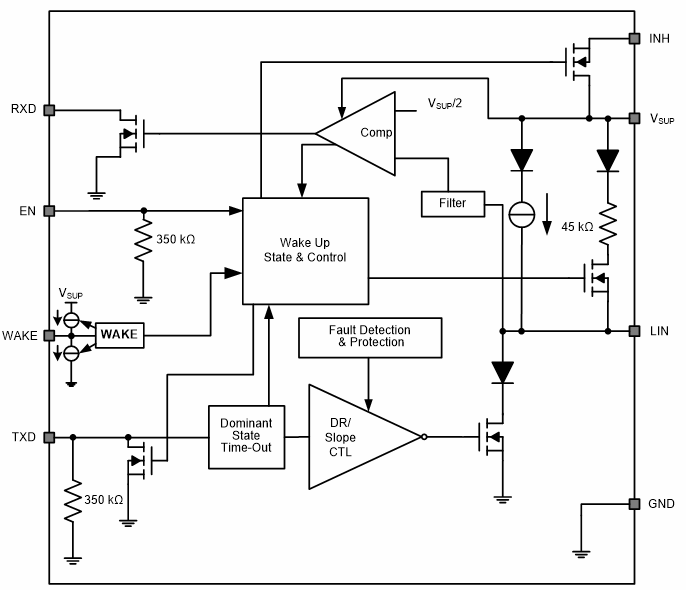

TLIN1021A-Q1 のトランスミッタは最大 20kbps のデータ・レートをサポートしています。本トランシーバは、TXD ピン経由で LIN バスの状態を制御し、オープン・ドレインの RXD 出力ピンでバスの状態を報告します。このデバイスは、電磁気放射 (EME) を低減するために電流制限付き波形整形ドライバを備えています。

TLIN1021A-Q1 は、広い入力電圧動作範囲によって 12V アプリケーションに対応するように設計されています。このデバイスは低消費電力スリープ・モードと、LIN、WAKE ピン、EN ピンによる低消費電力モードからのウェークアップをサポートしています。このデバイスを使用すると、ノードに存在する可能性がある各種電源を TLIN1021A-Q1 の INH 出力ピンで選択的に有効にすることで、バッテリの消費電流をシステム・レベルで低減できます。図 7-1 に、テキサス・インスツルメンツ TLIN1021A LIN トランシーバを使用して実装されている代表的なインターフェイスを示します。

図 7-1 標準的な LIN TLIN1021A トランシーバ

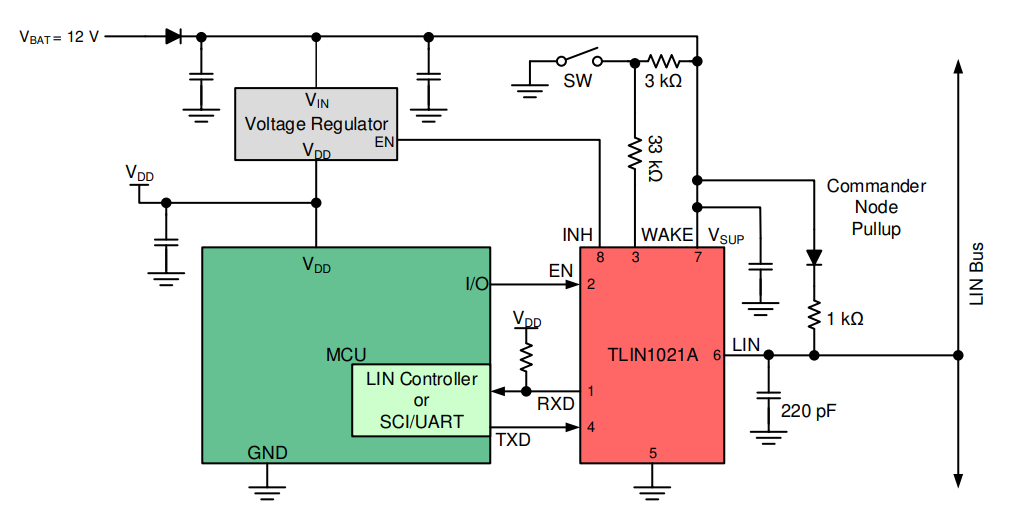

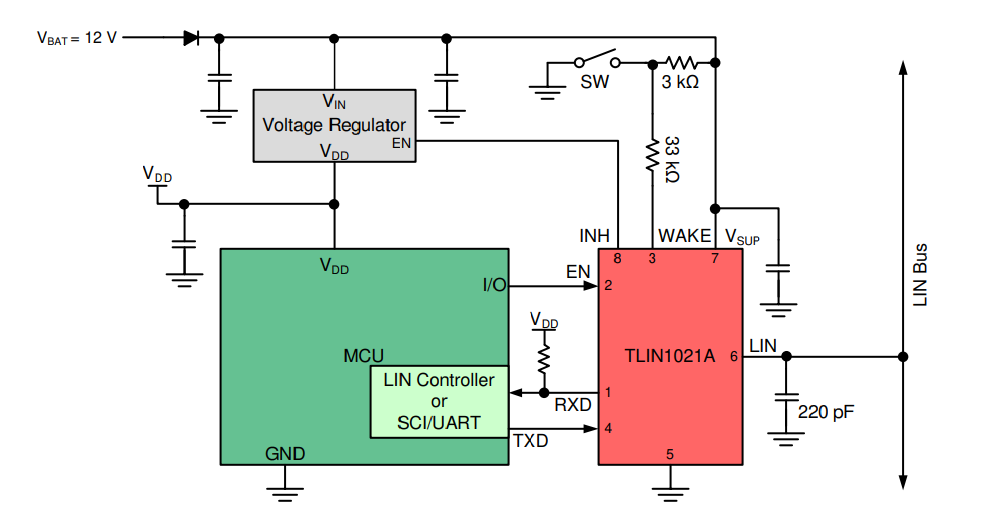

図 7-1 標準的な LIN TLIN1021A トランシーバ通信に必要なのは 1 本のワイヤのみであり、一般的に車両の配線ハーネスに含まれています。図 7-2 および 図 7-3 に、テキサス・インスツルメンツ TLIN1021A LIN トランシーバを使用して実装されている代表的なインターフェイスを示します。詳細については、TLIN1021 データシートを参照してください。

図 7-2 MSPM0G を使用した代表的な LIN アプリケーション (コマンダ)

図 7-2 MSPM0G を使用した代表的な LIN アプリケーション (コマンダ) 図 7-3 MSPM0G を使用した代表的な LIN アプリケーション (レスポンダ)

図 7-3 MSPM0G を使用した代表的な LIN アプリケーション (レスポンダ)