JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

6.3 DAC 設計の検討事項

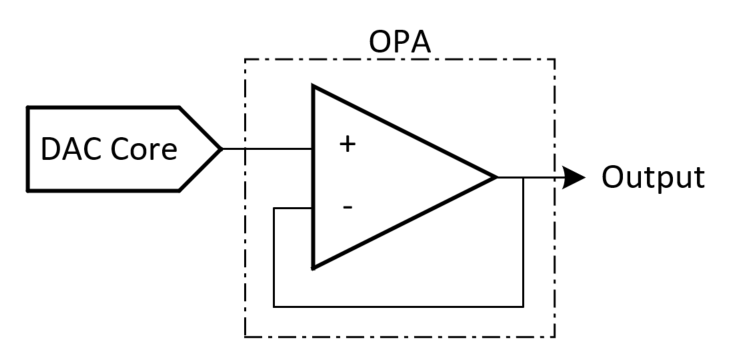

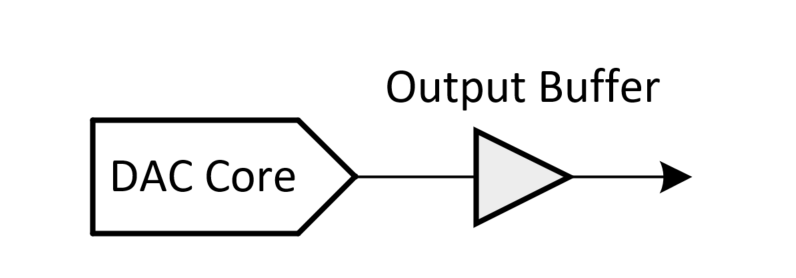

MSPM0G デバイスには、2 つの DAC モジュールが含まれています。8 ビットと 12 ビットDAC は基準電圧として使用でき、OPA と組み合わせて出力パッドを直接駆動することもできます。12 ビット DAC モジュールにはバッファが含まれているため、直接パッドに出力できます。ただし、8 ビット DAC モジュールは通常、OPA および COMP の内部基準電圧として使用されるため、外部ピンに出力するには、OPA をバッファ・モードに構成して駆動能力を向上させる必要があります。

すべてのデバイスにこれら 2 つの DAC モジュールが搭載されているわけではありません。詳細については、デバイス固有のデータシートをご覧ください。

図 6-4 8 ビット DAC のブロック図

図 6-4 8 ビット DAC のブロック図 図 6-5 8 ビット DAC および OPA 出力のブロック図

図 6-5 8 ビット DAC および OPA 出力のブロック図 図 6-6 12 ビット DAC 出力のブロック図

図 6-6 12 ビット DAC 出力のブロック図