JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

4.4 周波数クロック・カウンタ (FCC)

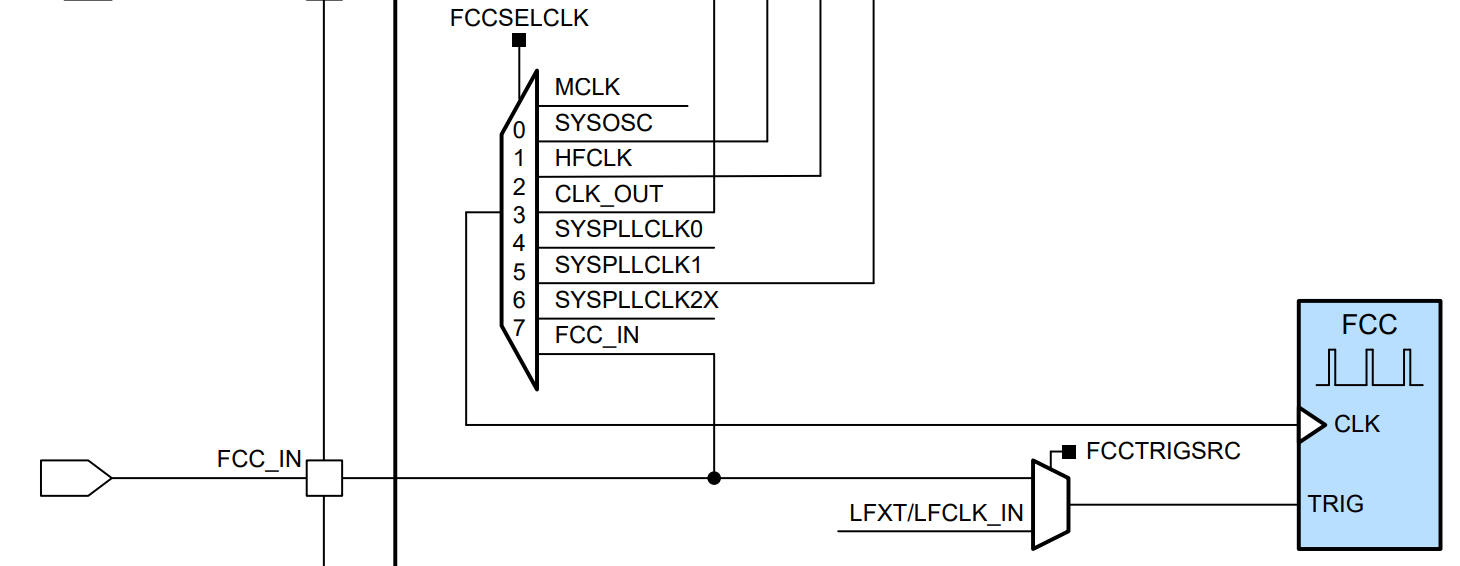

周波数クロック・カウンタ (FCC) を使用すると、デバイス上の各種発振器とクロックのテストとキャリブレーションを柔軟にインシステムで実施できます。FCC は、(2 次基準ソースから派生した) 既知の固定トリガ期間内に、選択したソース・クロックで観測されるクロック周期の数をカウントし、ソース・クロックの周波数を推定します。

図 4-7 MSPM0G 周波数クロック・カウンタのブロック図

図 4-7 MSPM0G 周波数クロック・カウンタのブロック図アプリケーション・ソフトウェアは、FCC を使用して、以下の発振器とクロックの周波数を測定できます。

- MCLK

- SYSOSC

- HFCLK

- CLK_OUT

- SYSPLLCLK0

- SYSPLLCLK1

- SYSPLLCLK2X

- 外部 FCC 入力 (FCC_IN)

注: 外部 FCC 入力 (FCC_IN 機能) は FCC クロック・ソースまたは FCC トリガ入力として使用できますが、同じ FCC キャプチャ中に両方の機能に使用することはできません。FCC クロック・ソースまたは FCC トリガとして構成する必要があります。