JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

9.3 トレース、ビア、その他の PCB コンポーネント

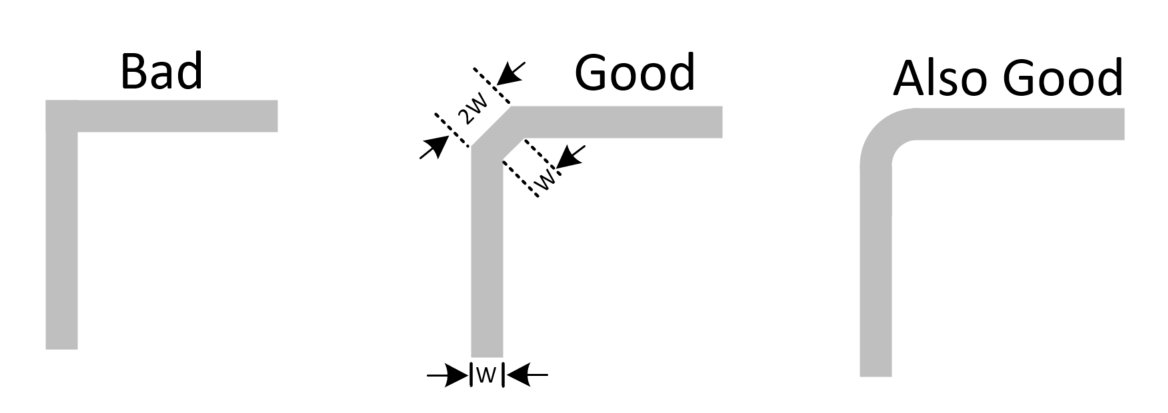

トレース内で直角を使用すると、より多くの放射線が発生する可能性があります。コーナーの領域で静電容量が増加し、特性インピーダンスが変化します。このインピーダンス変化は反射を引き起こします。トレース内で直角の曲げを避け、45 度のコーナーを 2 個以上使用してそれらを配線してください。インピーダンスの変化を最小限に抑えるために、図 9-3に示すように、最適な配線は円形の曲げです。

図 9-3 トレースを直角に曲げる不適切な方法と適切な方法

図 9-3 トレースを直角に曲げる不適切な方法と適切な方法クロストークを最小限に抑えるために、1 つの層の 2 つの信号間だけでなく、隣接する層の間にも 90 度で配線します。配線中にビアを使用する必要がある基板はより複雑ですが、ビアを使用する場合はインダクタンスと容量が追加されるため注意が必要であり、特性インピーダンスの変化により反射が発生します。また、ビアを使用するとトレースの長さも長くなります。差動信号を使用する場合は、両方のトレースにビアを使用するか、もう一方のトレースでも遅延を補償します。

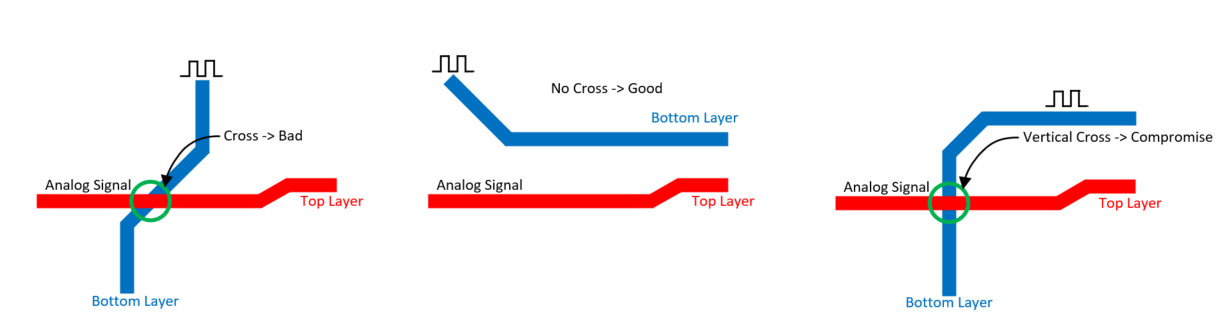

信号トレースの場合、特に比較的小さいアナログ信号 (センサ信号など) に高周波パルス信号が及ぼす影響に注意を払います。クロスオーバーが多すぎると、高周波信号の電磁ノイズがアナログ信号に結合され、信号の信号対雑音比が低くなり、信号の品質に影響を及ぼします。したがって、設計時に交差を避ける必要があります。ただし、確実に回避できない交差点が存在する場合は、電磁ノイズの干渉を最小限に抑えるために、垂直に交差することを推奨します。図 9-4に、このノイズを低減する方法を示します。

図 9-4 アナログ信号と高周波信号の不適切なクロス・トレースと適切なクロス・トレース

図 9-4 アナログ信号と高周波信号の不適切なクロス・トレースと適切なクロス・トレース