JAJA725B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

4.1 内部発振器

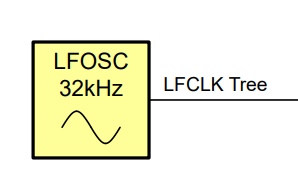

内部低周波数発振器 (LFOSC)

LFOSC はオンチップの低消費電力発振器で、32.768kHz の周波数に工場で調整されています。システムの低消費電力化に役立つ低周波数クロックを提供します。LFOSC は、低い温度範囲で使用する場合、より高い精度を実現できます。詳細については、デバイス固有のデータシートを参照してください。

図 4-1 MSPM0G シリーズ LFOSC

図 4-1 MSPM0G シリーズ LFOSC内部システム発振器 (SYSOSC)

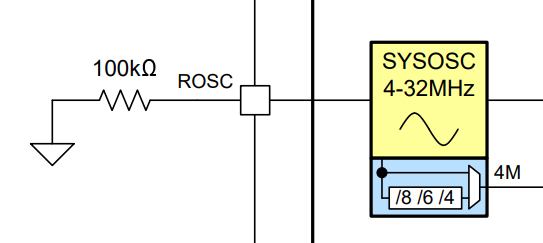

SYSOSC はオンチップの高精度で構成可能な発振器で、32MHz (ベース周波数) および 4MHz (低周波数) の出荷時に調整された周波数に加えて、24MHz または 16MHz でのユーザー・トリム動作もサポートしています。コードの実行と処理性能のために CPU を高速で動作させるための高周波クロックを提供します。

図 4-2 MSPM0G シリーズ SYSOSC

図 4-2 MSPM0G シリーズ SYSOSCSYSOSC 周波数補正ループ

この発振器の追加ハードウェア設定は、ROSC ピンと VSS の間に実装される外付け抵抗であり、温度範囲全体で ±2.5% の基本精度から SYSOSC を増加させます。

SYSOSC アプリケーション全体の精度は、以下の誤差ソースを組み合わせて総合誤差を求めることで決定されます。

- ROSC 基準抵抗の誤差 (許容誤差と温度ドリフトによる)

- FCL モードでの SYSOSC 回路の誤差 (-40℃~85℃で ±0.75%、-40℃~125℃で ±0.90%)

表 4-1 に、2 つの温度範囲にわたる 2 つの異なる ROSC 抵抗仕様について、SYSOSC アプリケーションの精度を計算する方法を示します。詳細については、各デバイスの TRM をご覧ください。

| 周囲温度 (TA) | -40 ≤ TA ≤ 125℃ | -40 ≤ TA ≤ 85℃ | ||

|---|---|---|---|---|

| ROSC 抵抗パラメータ | ±0.1% 25ppm/℃ | ±0.5% 25ppm/℃ | ±0.1% 25ppm/℃ | ±0.5% 25ppm/℃ |

| 公称 ROSC 抵抗 (ROSCnom) | 100kΩ | |||

| 最大 ROSC 抵抗 (25℃時) | 100.1kΩ | 100.5kΩ | 100.1kΩ | 100.5kΩ |

| 最小 ROSC 抵抗 (25℃時) | 99.9kΩ | 99.5kΩ | 99.9kΩ | 99.5kΩ |

| ROSC 抵抗 TCR | 25ppm/℃ | |||

| ROSC 温度ドリフト | -0.16%~0.25% | -0.16%~0.15% | ||

| 最大 ROSC 抵抗 (高温時) (ROSCmax) | 100.35kΩ | 100.75kΩ | 100.25kΩ | 100.65kΩ |

| 最小 ROSC 抵抗 (低温時) (ROSCmin) | 99.74kΩ | 99.34kΩ | 99.74kΩ | 99.34kΩ |

| ROSC 抵抗誤差 (高温) (ROSCerr+) | +0.35% | +0.75% | +0.25% | +0.65% |

| ROSC 抵抗誤差 (低温) (ROSCerr-) | -0.26% | -0.66% | -0.26% | -0.66% |

| SYSOSC 回路エラー (SYSOSCerr) | ±0.9% | ±0.75% | ||

| 総合精度 (TOTerr-、TOTerr+) | -1.2%~+1.3% | -1.6%~+1.7% | -1.0%~+1.0% | -1.4%~+1.4% |

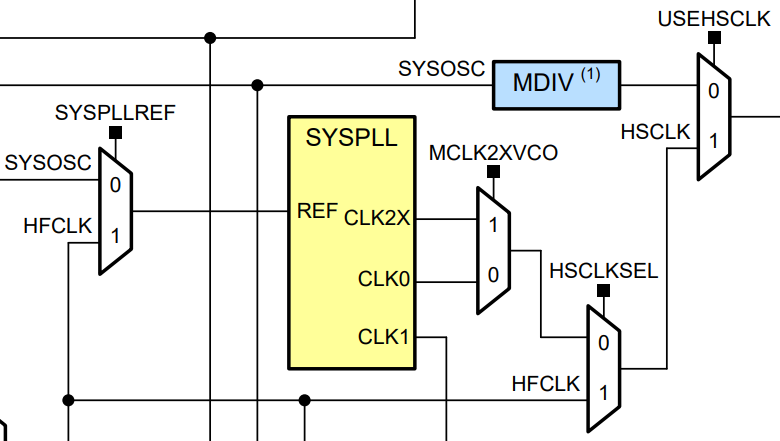

システム・フェーズ・ロック・ループ (SYSPLL)

SYSPLL は、プログラム可能な周波数を備えたシステム・フェーズ・ロック・ループであり、MSPM0G シリーズの最高速度 (80MHz) を達成するために使用されます。

図 4-3 MSPM0G SYSPLL 回路

図 4-3 MSPM0G SYSPLL 回路