JAJA735 february 2023

3.4 各種アナログ・ペリフェラル間の内部接続

MSPM0 デバイス内の内部アナログ接続は、ソフトウェアで構成できます。以下の例は、各種の使用事例のためのアナログ機能を簡単かつ柔軟に構成するための MSPM0 デバイス内の内部経路を示しています。

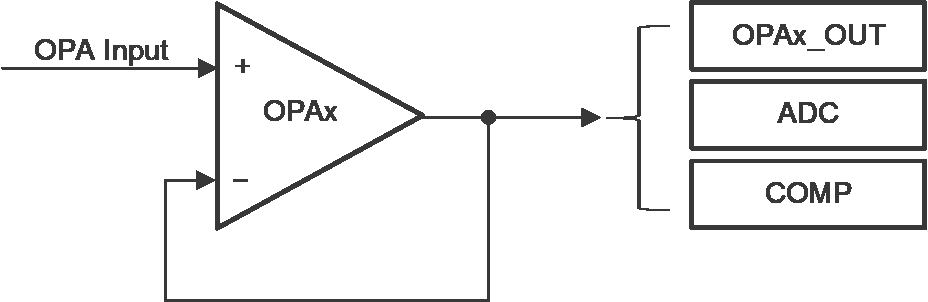

- 入力信号を増幅するために、OPA を ADC と COMP に配線します (図 3-5を参照)。

図 3-5 ADC および コンパレータとの OPA の接続

図 3-5 ADC および コンパレータとの OPA の接続OPA チョッピング・モードを使うと、オフセット電圧およびドリフト性能を大幅に向上させることができます。OPA を ADC に接続する際に、チョッピング・モードが必要な場合、OPA 内部の標準チョッピング以外に、ADC 補助チョッピング・モードも使えます。

- バイアス生成として、COMP の 8 ビット DAC を OPA に、または 12 ビット DAC を OPA に配線します。

一部の MSPM0G デバイスは、デバイス内のスタンドアロン・ペリフェラルとして 12 ビット DAC をサポートしています。バイアス電圧を生成するため、この DAC を OPA 入力に直接接続できます (図 3-6 を参照)。

図 3-6 12 ビット DAC と OPA との接続

バイアス電圧を生成できるのは、12 ビット DAC のみではありません。コンパレータの 8 ビット DAC も OPA に接続できます (図 3-7 を参照)。

図 3-7 コンパレータの 8 ビット DAC と OPA との接続

- 入力信号を増幅するため、GPAMP 出力を ADC および OPA に接続します。

GPAMP からその他のアナログ・ペリフェラル (OPA など) に直接接続することもできます。ADC に接続する場合、標準および ADC 補助チョッピング・モードも GPAMP 内でサポートされています (図 3-8を参照)。

図 3-8 GPAMP と ADC および OPA との接続

図 3-8 GPAMP と ADC および OPA との接続