JAJS963E August 2002 – March 2024 DS90LT012A , DS90LV012A

PRODUCTION DATA

2 概要

DS90LV012A および DS90LT012A は、超低消費電力、低ノイズ、高データ レートを必要とするアプリケーション用に設計されたシングル CMOS 差動ライン レシーバです。本デバイスは、低電圧差動スイング (LVDS) テクノロジを利用して 400Mbps (200MHz) を超えるデータ レートをサポートするよう設計されています。

DS90LV012A および DS90LT012A は低電圧 (標準値 350mV) の差動入力信号を受信し、3V CMOS 出力レベルに変換します。また、レシーバは開放、短絡、終端 (100Ω) の入力フェイルセーフもサポートします。すべてのフェイルセーフ条件において、レシーバの出力は High になります。DS90LV012A のピン配置は、PCB レイアウトが容易になるよう設計されています。DS90LT012A は、ポイント ツー ポイント アプリケーション用の入力ライン終端抵抗を内蔵しています。

DS90LV012A および DS90LT012A と、対になる LVDS ライン ドライバは、高速インターフェイス アプリケーション用の消費電力の大きい PECL/ECL デバイスに代わる新たな選択肢です。

製品情報

| 部品番号 | パッケージ (1) | 本体サイズ (公称) |

|---|---|---|

| DS90LV012A | WSON-8、SOT-23、DBV | 3.00mm × 3.00mm |

| DS90LT012A | WSON-8、SOT-23、DBV | 3.00mm × 3.00mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

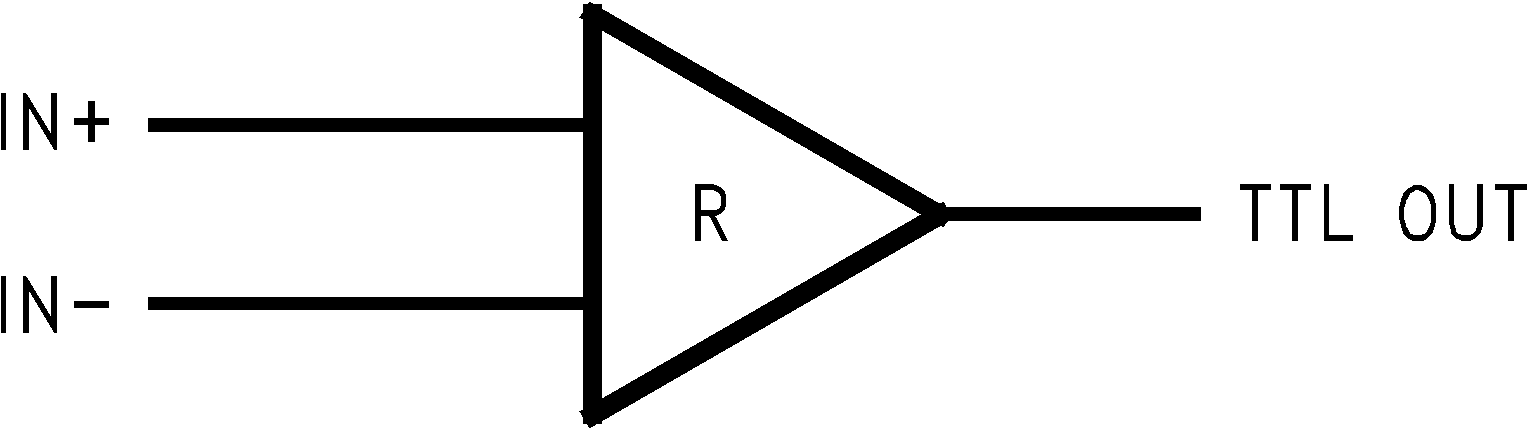

DS90LV012A の上面図

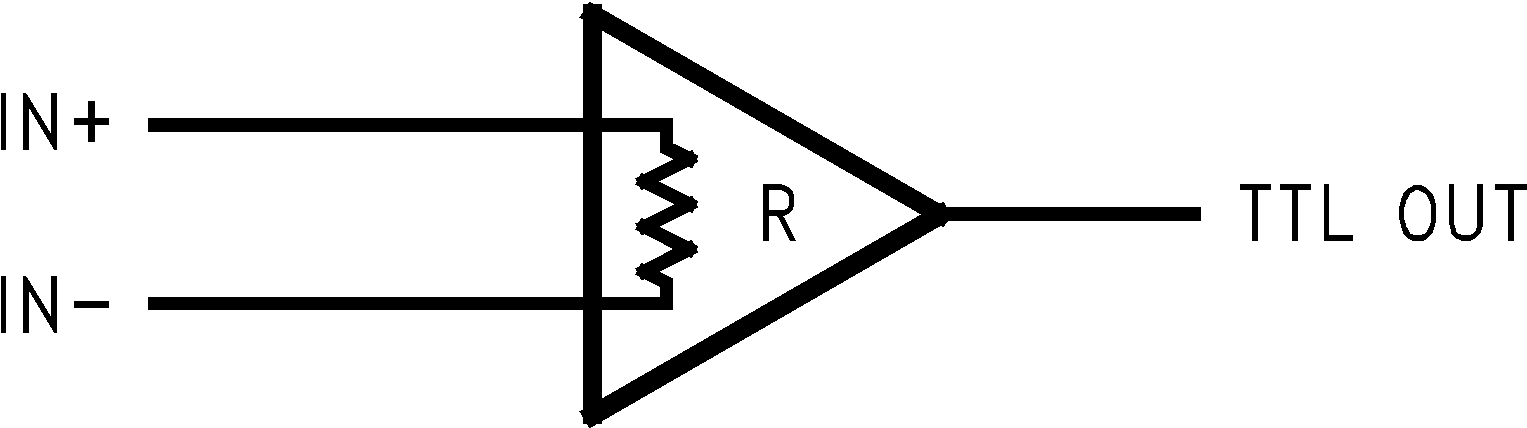

DS90LV012A の上面図 DS90LT012A の上面図

DS90LT012A の上面図