JAJSBR5H February 2012 – June 2018 TLV62130 , TLV62130A

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2 Typical Application

- 9.3 System Examples

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

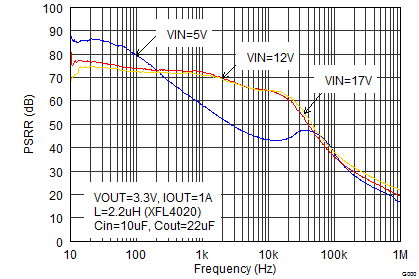

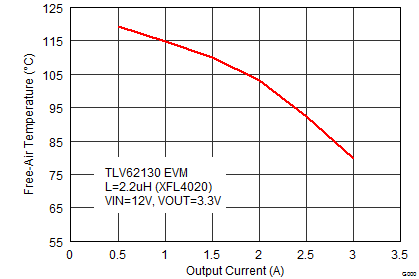

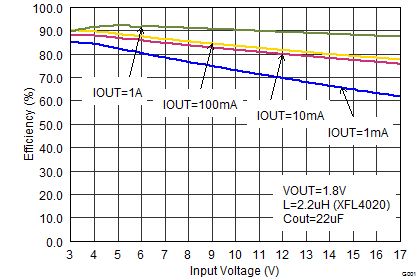

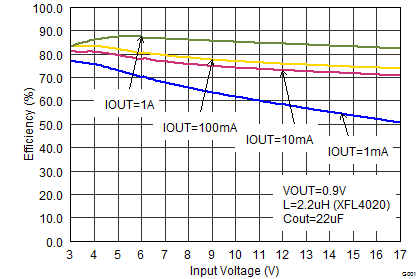

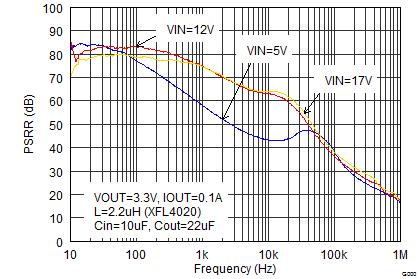

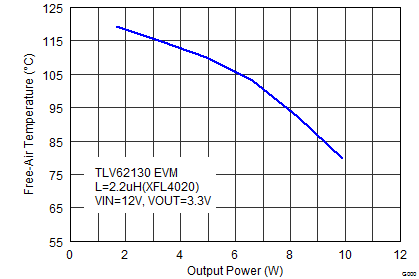

9.2.3 Application Curves

VIN = 12 V, VOUT = 3.3 V, TA = 25°C, (unless otherwise noted)

| FSW=Low |

| Iout=1A |

Figure 28. PWM-PSM-Transition

Figure 28. PWM-PSM-Transition

(VIN = 12 V, VOUT=3.3 V with 50 mV/Div)

Figure 30. Load Transient Response of Figure 29,

Figure 30. Load Transient Response of Figure 29,

Rising Edge

Figure 32. Startup into 100 mA

Figure 32. Startup into 100 mA  Figure 34. Typical Operation in PWM Mode

Figure 34. Typical Operation in PWM Mode

(IOUT = 1 A)

| FSW=Low |

| Iout=0.1A |

Figure 29. Load Transient Response

Figure 29. Load Transient Response

(IOUT = 0.5 to 3 to 0.5 A)

Figure 31. Load Transient Response of Figure 29,

Figure 31. Load Transient Response of Figure 29,

Falling Edge

Figure 33. Startup into 3 A

Figure 33. Startup into 3 A  Figure 35. Typical Operation in Power Save Mode

Figure 35. Typical Operation in Power Save Mode

(IOUT = 10 mA)

sp