JAJSFO0G september 2012 – october 2020 SN65DSI85

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Abstract

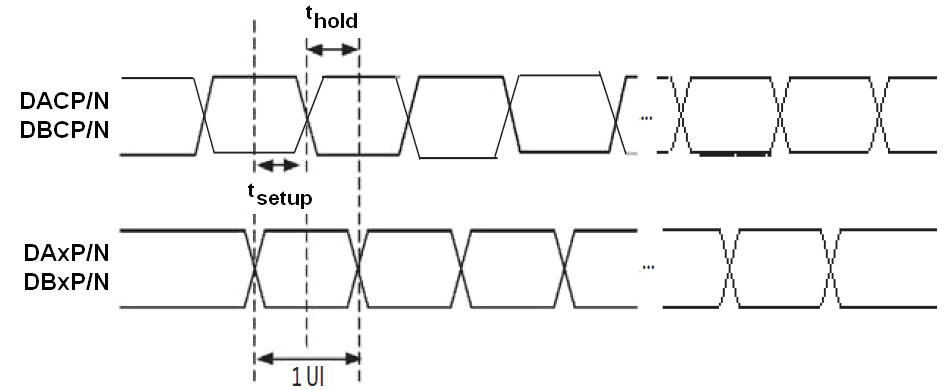

Figure 7-1 SN65DSI85 FlatLink™ Timing Definitions

Figure 7-1 SN65DSI85 FlatLink™ Timing Definitions

A. See the ULPS section of the data sheet for the ULPS entry and exit sequence.

B. ULPS entry and exit protocol and timing requirements must be met per MIPI® DPHY specification.

Figure 7-2 ULPS Timing Definition Figure 7-3 DSI HS Mode Receiver Timing Definitions

Figure 7-3 DSI HS Mode Receiver Timing Definitions