-

TPS7H1210-SEP -16.5V、1A、負リニア・レギュレータ、宇宙用強化プラスチック

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- 重要なお知らせ

DATA SHEET

TPS7H1210-SEP -16.5V、1A、負リニア・レギュレータ、宇宙用強化プラスチック

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- VID (Vendor Item Drawing) V62/21616 が利用可能

- 総照射線量 (TID) 耐性 = 30krad (Si)

- すべてのウェハー・ロットについて、20krad(Si) までの TID RLAT (放射線ロット受け入れテスト)

- シングルイベント効果 (SEE) の特性

- シングルイベント・ラッチアップ (SEL)、シングルイベント・バーンアウト (SEB)、シングルイベント・ゲート・ラプチャー (SEGR) の、線エネルギー付与 (LET) に対する耐性 = 43MeV-cm2/mg

- シングルイベント機能割り込み (SEFI) およびシングルイベント過渡 (SET) の LET に対する耐性 = 43MeV-cm2/mg

- 低ノイズ:13.7μVRMS (標準値、10Hz~100kHz)

- 高い電源除去比、PSRR (VIN = -6V、VOUT = -5V、IOUT = 1A での標準値):

- 100Hz 時に 61dB

- 100kHz 時に 61dB

- 1MHz 時に 41dB

- 入力電圧範囲:-3V~-16.5V

- 調整可能な出力:-1.2V~-15.5V

- 最大 1A の出力電流

- 10µF 以上のセラミック出力コンデンサで安定動作

- 電流制限とサーマル・シャットダウン保護機能を内蔵

- 宇宙向け強化プラスチック (SEP)

- 管理されたベースライン

- 金ボンド・ワイヤ

- NiPdAu リード仕上げ

- 単一のアセンブリ / テスト施設

- 単一の製造施設

- 軍用温度範囲:-55℃~125℃

- 長い製品ライフ・サイクル

- 製品変更通知期間 (PCN) の延長

- 製品のトレーサビリティ

- モールド・コンパウンドの改良による低いガス放出

2 アプリケーション

- 低軌道 (LEO) 衛星用途のサポート

- 衛星用電源システム (EPS)

- アナログ回路の電源

- データ・コンバータ:ADC と DAC (A/D コンバータと D/A コンバータ)

- オペアンプ (演算増幅器)

- イメージング・センサ

- DC-DC コンバータのポスト・レギュレーションおよびリップル・フィルタ処理

- 耐放射線が強化された、制約のある宇宙分野向けの超クリーンなアナログ電源

3 概要

TPS7H1210-SEP 負電圧リニア・レギュレータは、1A の最大負荷を供給できる低ノイズ、高 PSRR のレギュレータです。

このレギュレータには、CMOS ロジックレベル互換のイネーブル・ピン (EN) が搭載されており、ユーザーがカスタマイズ可能なパワー・マネージメント方式を実現できます。その他の機能として、電流制限機能とサーマル・シャットダウン機能が内蔵されており、障害状態時にデバイスとシステムが保護されます。

TPS7H1210-SEP デバイスは、システム性能を最大限に高めるためにクリーンな電源レールが決定的に重要な、高精度、低ノイズのアプリケーションを主な対象として、バイポーラ・テクノロジで設計されています。したがって、オペアンプ、ADC、DAC、その他の高性能アナログ回路への電力供給に理想的です。

そのほか、TPS7H1210-SEP デバイスは、DC/DC コンバータのポスト・レギュレーションに適しています。DC/DC スイッチング変換に本質的に付随する出力電圧リップルをフィルタ処理し、影響を受けやすいデバイスや RF アプリケーションにおいて、最大のシステム性能が保証されます。

デバイス情報

| 部品番号 (1) | グレード | パッケージ (2) |

|---|---|---|

| TPS7H1210MRGWSEP | 20krad(Si) RLAT、30krad(Si) 特性 | VQFN (20) 5.00mm × 5.00mm 質量 = 83.6mg |

| TPS7H1210EVM | 評価ボード | EVM |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

(2) 寸法と質量は公称値です。

代表的なアプリケーション回路図

代表的なアプリケーション回路図4 Revision History

| DATE | REVISION | NOTES |

|---|---|---|

| November 2021 | * | Initial Release |

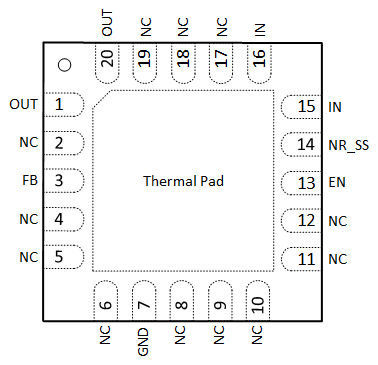

5 Pin Configuration and Functions

Figure 5-1 RGW Package,20-Pin VQFN(Top View)

Figure 5-1 RGW Package,20-Pin VQFN(Top View)Table 5-1 Pin Functions

| PIN | I/O(1) | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| EN | 13 | I | Enable. This dual-polarity pin turns the regulator on when |VEN| ≥ 2 V. The EN pin can be connected to IN if not used. If VEN is negative polarity, then keep |VEN| ≤ |VIN|. |

| FB | 3 | I | Feedback. This pin is the input to the control-loop error amplifier. It is used to set the output voltage of the device and is normally equal to VREF (–1.182 V, typical) during operation. |

| GND | 7 | — | Ground. |

| IN | 15, 16 | I | Input supply. It is recommended to connect a 10-µF capacitor from IN to GND (as close to the device as possible). |

| NC | 2, 4–6, 8–12, 17–19 | — | No connect. This pin is not internally connected. It is recommended to connect these pins to GND to prevent charge buildup; however, these pins can also be left open or tied to any voltage between GND and VIN. |

| NR_SS | 14 | — | Noise reduction and soft start. A capacitor connected from this pin to GND controls the soft-start function and allows RMS noise to be reduced to very low levels. TI recommends connecting a 100-nF capacitor from NR_SS to GND (as close to the device as possible) to filter the noise generated by the internal band gap and maximize AC performance. |

| OUT | 1, 20 | O | Output of the regulator. A capacitor greater than or equal to 10 µF must be tied from this pin to ground to ensure stability. TI recommends connecting a 47-µF ceramic capacitor from OUT to GND (as close to the device as possible) to maximize AC performance. |

| Thermal Pad |

— | — | Connect the thermal pad to a large-area ground plane. The thermal pad is not internally grounded and it must be externally tied to GND for proper operation. |

(1) I = Input, O = Output, — =

Other

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Input voltage | IN to GND | –35 | 0.3 | V |

| FB to GND | –2 | 0.3 | V | |

| FB to IN | –0.3 | 35 | V | |

| EN to GND | –35 | 10 | V | |

| NR_SS to IN | –0.3 | 35 | V | |

| NR_SS to GND | –2 | 0.3 | V | |

| Output voltage | OUT to GND | –33 | 0.3 | V |

| OUT to IN | –0.3 | 35 | V | |

| Output current | Peak output | Internally limited | ||

| Operating virtual junction temperature | TJ | –55 | 150 | °C |

| Storage temperature | Tstg | –65 | 150 | °C |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.