JAJSMP8C May 2023 – June 2024 OPT4001-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Register Maps

-

8 Application and Implementation

- 8.1 Application Information

- 8.2 Typical Application

- 8.3 Best Design Practices

- 8.4 Power Supply Recommendations

- 8.5 Layout

- 9 デバイスおよびドキュメントのサポート

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

6.4.2 Interrupt Modes of Operation

The device has an interrupt reporting system that allows the processor connected to the I2C bus to go to sleep, or otherwise ignore the device results, until a user-defined event occurs that requires possible action. Alternatively, this same mechanism can also be used with any system that can take advantage of a single digital signal that indicates whether the light is above or below levels of interest.

The INT pin (only available on USON variant) has an open-drain output, which requires the use of a pullup resistor. This open-drain output allows multiple devices with open-drain INT pins to connect to the same line, thus creating a logical NOR or AND function between the devices. The polarity of the INT pin can be controlled by the INT_POL register.

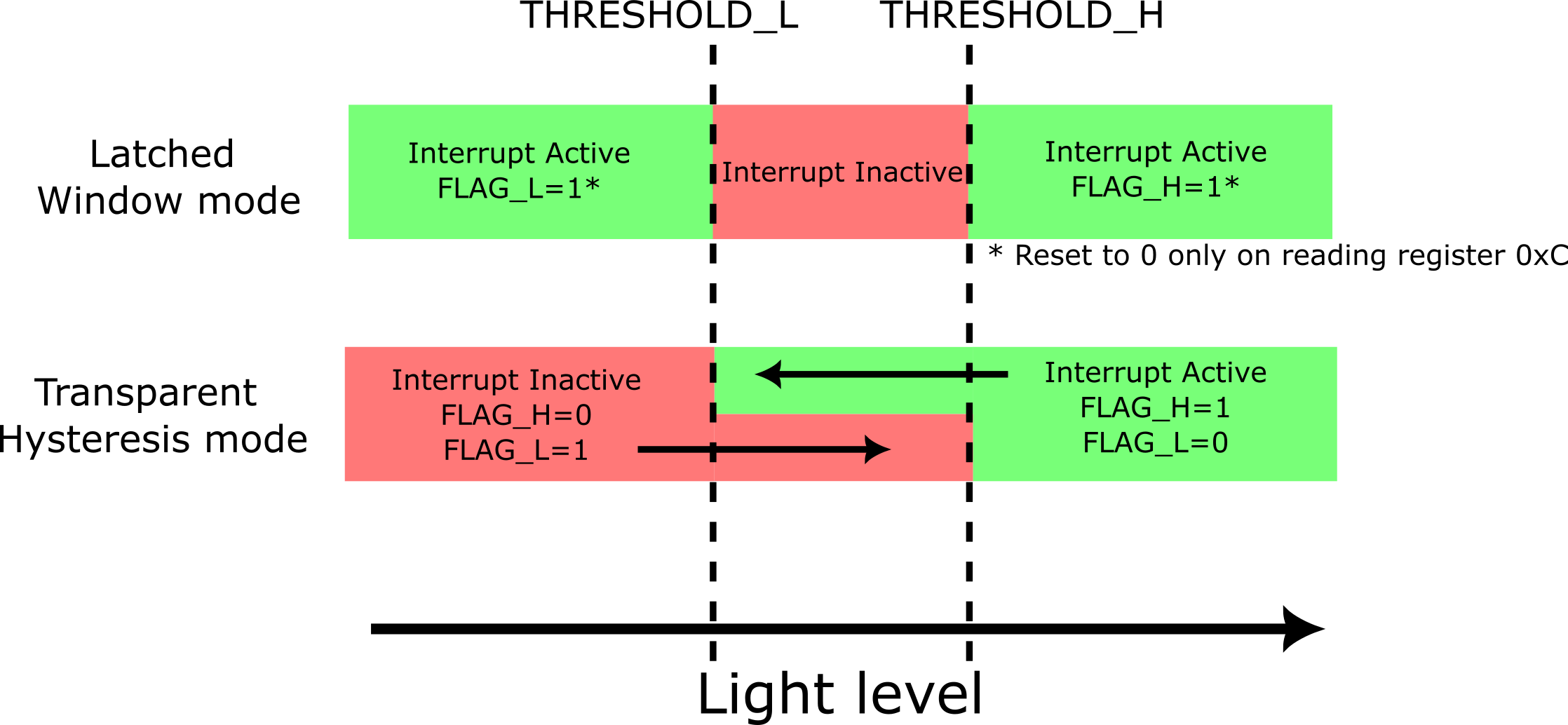

There are two major types of interrupt reporting mechanism modes: latched window comparison mode and transparent hysteresis comparison mode. The LATCH configuration register controls which of these two modes is used. Table 6-1 and Figure 6-4 summarize the function of these two modes. Additionally, the INT pin can either be used to indicate a fault in one of these modes (INT_CFG = 0) or to indicate a conversion completion (INT_CFG > 0). Table 6-2 details this functionality.

Figure 6-4 Interrupt Pin Status (INT_CFG = 0 Setting) and Register Flag Behavior

Figure 6-4 Interrupt Pin Status (INT_CFG = 0 Setting) and Register Flag Behavior | LATCH SETTING | INT PIN STATE (WHEN INT_CFG=0) | FLAG_H VALUE | FLAG_L VALUE | LATCHING BEHAVIOR |

|---|---|---|---|---|

| 0: Transparent hysteresis mode | The INT pin indicates if measurement is above (INT active) or below (INT inactive) the threshold. If measurement is between the high and low threshold values, then the previous INT value is maintained. This mode prevents the INT pin from repeated toggling when the measurement values are close to the threshold. | 0: If measurement is below the low limit 1: If measurement is above the high limit If measurement is between the high and low limits, the previous value is maintained. | 0: If measurement is above the high limit 1: If measurement is below the low limit If measurement is between the high and low limits, the previous value is maintained. | Not latching: Values are updated after each conversion |

| 1: Latched window mode | The INT pin becomes active if the measurement is outside the window (above the high threshold or below the low threshold). The INT pin does not reset and returns to the inactive state until the 0xC is register read. | 1: If measurement is above the high limit | 1: If measurement is below the low limit | Latching: The INT pin, FLAG_H, and FLAG_L values do not reset until the 0x0C register is read. |

The THRESHOLD_H, THRESHOLD_L, LATCH, and FAULT_COUNT registers control the interrupt behavior. As shown in Table 6-1, the LATCH field setting provides a choice between the latched window mode and transparent hysteresis mode. Interrupt reporting can be observed on the INT pin (for USON variant only), the FLAG_H, and the FLAG_L registers.

Results from comparing the current sensor measurements with the THRESHOLD_H and THRESHOLD_L registers are referred to as fault events. See the Threshold Detection Calculations section for the calculations to set these registers. The FAULT_COUNT register dictates the number of continuous fault events required to trigger an interrupt event and subsequently change the state of the interrupt reporting mechanisms. For example, with a FAULT_COUNT value of 2 corresponding to four fault counts, the INT pin (USON variant only), FLAG_H, and FLAG_L states shown in Table 6-1 are not realized unless four consecutive measurements are taken that satisfy the fault condition.

The INT pin function (for USON variant only) listed in Table 6-1 is valid only when INT_CFG = 0. As described in Table 6-2, the INT pin function can be changed to indicate an end of conversion or FIFO full state. The FLAG_H and FLAG_L registers continue to behave as listed in Table 6-1, even while INT_CFG > 0. The polarity of the INT pin is controlled by the INT_POL register.

| INT_CFG SETTING | INT PIN FUNCTION |

|---|---|

| 0 | As per Table 6-1 |

| 1 | INT pin asserted with a 1-µs pulse duration after every conversion |

| 3 | INT pin asserted with a 1-µs pulse duration every four conversions to indicate the FIFO is full |