JAJSO15A february 2022 – june 2023 LMK1D1208I

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

10.2.3 Application Curves

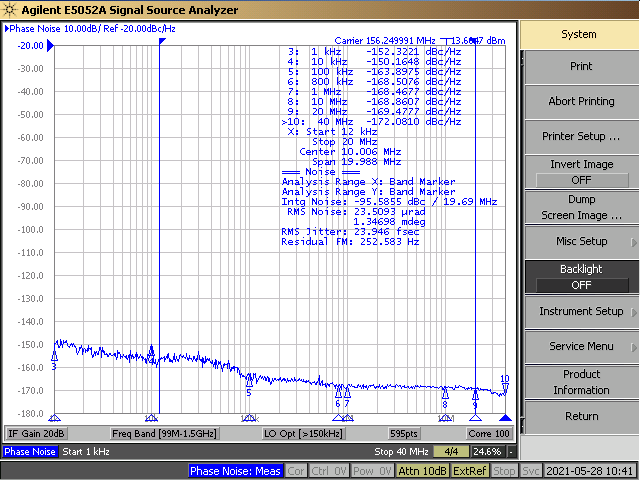

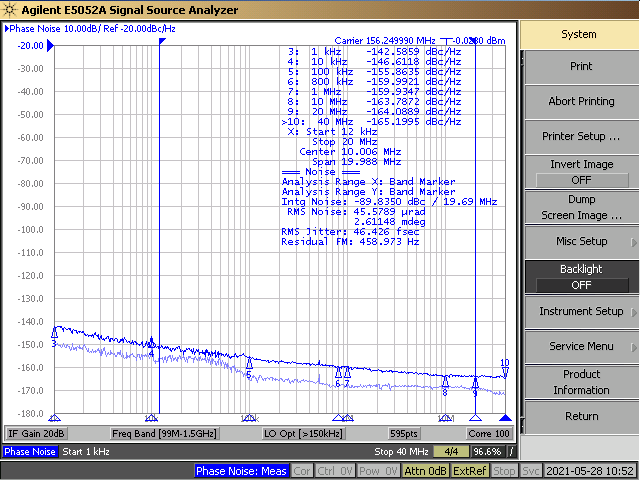

The following graphs show the low additive noise of the LMK1D1208I. The low noise 156.25-MHz source with 24-fs RMS jitter shown in Figure 10-2 drives the LMK1D1208I, resulting in 46.4-fs RMS when integrated from 12 kHz to 20 MHz (Figure 10-3). The resultant additive jitter is a low 39.7-fs RMS for this configuration.

| Reference signal is low-noise Rohde and Schwarz SMA100B |

Figure 10-3 LMK1D1208I Output Phase Noise, 156.25 MHz, 46.4-fs RMS (12 kHz to 20

MHz)

Figure 10-3 LMK1D1208I Output Phase Noise, 156.25 MHz, 46.4-fs RMS (12 kHz to 20

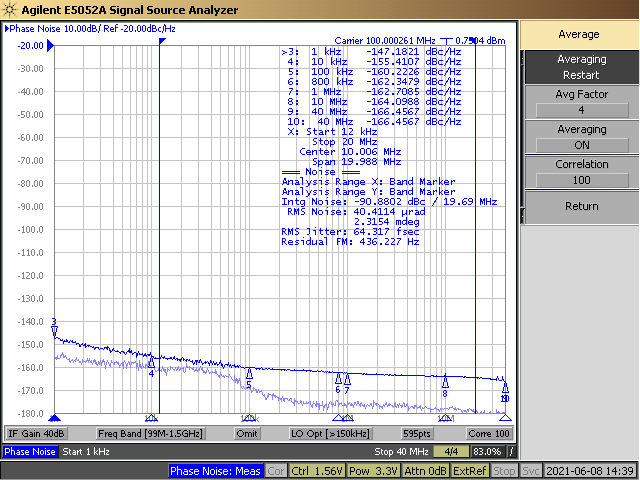

MHz)Figure 10-4 shows the low close-in phase noise of the LMK1D1208I device. The LMK1D1208I has excellent flicker noise as a result of superior process technology and design. This enables their use for clock distribution in radar systems, medical imaging systems etc which require ultra-low close-in phase noise clocks.

Figure 10-4 LMK1D1208I Output Phase Noise, 100 MHz, 1-kHz Offset: –147 dBc/Hz

Figure 10-4 LMK1D1208I Output Phase Noise, 100 MHz, 1-kHz Offset: –147 dBc/Hz