JAJSOB8B March 2023 – April 2024 ADS127L21

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 ピン構成および機能

- 5 仕様

- 6 パラメータ測定情報

-

7 詳細説明

- 7.1 概要

- 7.2 機能ブロック図

- 7.3 機能説明

- 7.4 デバイスの機能モード

- 7.5 プログラミング

- 8 レジスタ マップ

- 9 アプリケーションと実装

- 10デバイスおよびドキュメントのサポート

- 11改訂履歴

- 12メカニカル、パッケージ、および注文情報

9.2.3.3 アプリケーション曲線

以下の図は、SPICE ベースのアナログ シミュレーション プログラムである TINA-TI™ によって生成されたものです。THS4551 の SPICE モデルは、THS4551 の製品フォルダからダウンロードできます。

アンチエイリアス フィルタの周波数応答、およびアンチエイリアス フィルタと ADC の合計応答を、図 9-9 に示します。この図に示すように、このフィルタはナイキスト周波数から 12.8MHz の fMOD 周波数まで、90dB のストップバンド減衰を実現します。

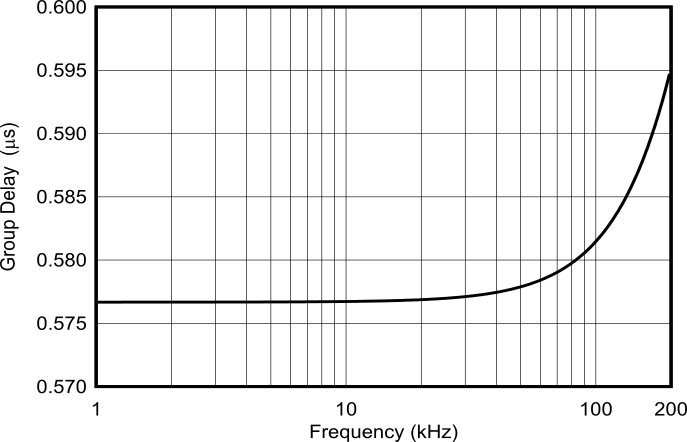

アナログ フィルタの群遅延を、図 9-10 に示します。この群遅延は 0.575μs で、ADC デジタル フィルタの群遅延 85μs (34 / fDATA) と比較して小さくなります。アナログ フィルタの群遅延の直線性は 0.017μs で、165kHz のパス バンドのエッジでピークになります。

図 9-9 アンチエイリアス フィルタの周波数応答

図 9-9 アンチエイリアス フィルタの周波数応答 図 9-10 アンチエイリアス フィルタの群遅延

図 9-10 アンチエイリアス フィルタの群遅延アンチエイリアス フィルタ回路のノイズ密度、ADC のノイズ密度、フィルタと ADC の合計ノイズ密度を、図 9-11 に示します。ノイズ密度は、周波数に対してプロットされた帯域幅の √Hz あたりのノイズ電圧です。

1Hz のスタート周波数から ADC の最終帯域幅までの合計ノイズを、図 9-12 に示します。200Hz 未満では、ノイズの大部分は THS4551 アンプの 1 / f 電圧および電流ノイズです。200Hz を超えると、ノイズの大部分は ADC ノイズになります。165kHz 帯域幅でのフィルタと ADC の合計ノイズは 11.8μV で、目標値の 12μV を満たしています。

THS4551 の代わりに THP210 入力ドライバを使用すると、低周波数のノイズ性能を向上できます。詳細については、THP210 と ADS127L11 の性能に関するアプリケーション ノートを参照してください。

図 9-11 ノイズ密度

図 9-11 ノイズ密度 図 9-12 合計ノイズ

図 9-12 合計ノイズ