Data Sheet

SN74AHC08Q-Q1 車載用クワッド 2 入力正論理 AND ゲート

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- 車載アプリケーション認定済み

- 2V~5.5V の VCC で動作

- EPIC™ (Enhanced-Performance Implanted CMOS) プロセス

- JESD 17 準拠で 250mA 超のラッチアップ性能

2 概要

このデバイスはクワッド 2 入力正論理 AND ゲートであり、ブール関数 Y + A • B または Y = A + B を正論理で実行します。

パッケージ情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| SN74AHC08Q-Q1 | D (SOIC、14) | 8.65mm × 6mm | 8.65mm × 3.9mm |

| PW (TSSOP、14) | 5.00mm × 6.4mm | 5mm × 4.4mm | |

| BQA (WQFN、14) | 3mm × 2.5mm | 3mm × 2.5mm |

(1) 詳細については、セクション 9 を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

論理図 (正論理)

論理図 (正論理)3 Pin Configuration and Functions

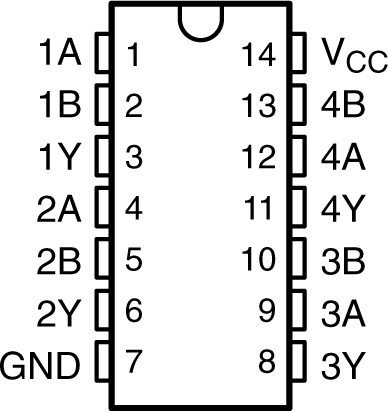

Figure 3-1 D or PW Package, 14-Pin

SOIC or TSSOP (Top View)

Figure 3-1 D or PW Package, 14-Pin

SOIC or TSSOP (Top View) Figure 3-2 BQA Package, 14-Pin WQFN

(Top View)

Figure 3-2 BQA Package, 14-Pin WQFN

(Top View)Table 3-1 Pin Functions

| PIN | TYPE | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| 1A | 1 | Input | Channel 1, Input A |

| 1B | 2 | Input | Channel 1, Input B |

| 1Y | 3 | Output | Channel 1, Output Y |

| 2A | 4 | Input | Channel 2, Input A |

| 2B | 5 | Input | Channel 2, Input B |

| 2Y | 6 | Output | Channel 2, Output Y |

| GND | 7 | — | Ground |

| 3Y | 8 | Output | Channel 3, Output Y |

| 3A | 9 | Input | Channel 3, Input A |

| 3B | 10 | Input | Channel 3, Input B |

| 4Y | 11 | Output | Channel 4, Output Y |

| 4A | 12 | Input | Channel 4, Input A |

| 4B | 13 | Input | Channel 4, Input B |

| VCC | 14 | — | Positive Supply |

| Thermal Information | — | The thermal pad can be connected to GND or left floating. Do not connect to any other signal or supply. | |