JAJSV36D August 1995 – July 2024 SN54ACT10 , SN74ACT10

PRODUCTION DATA

2 概要

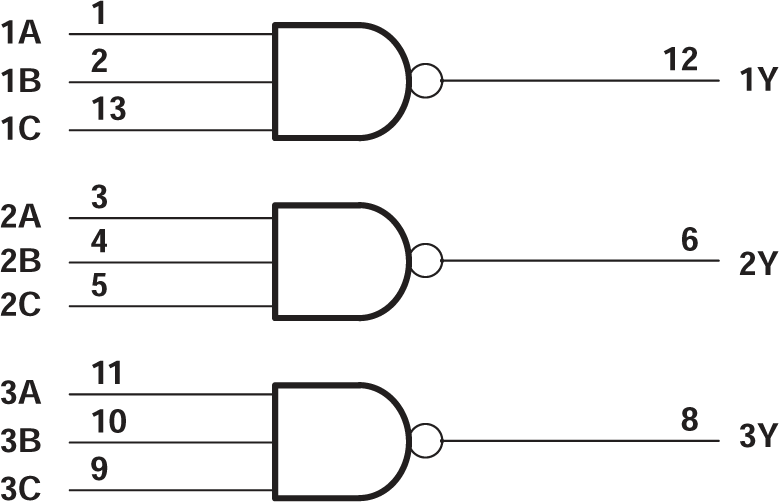

’ACT10 デバイスには、3 つの独立した 3 入力 NAND ゲートが内蔵されています。ブール関数 Y = A • B • C つまり、Y = A + B + C を正論理で実行します。

製品情報

| 部品番号 | パッケージ (1) | パッケージ サイズ(2) | 本体サイズ (3) |

|---|---|---|---|

| SNx4ACT10 | D (SOIC、14) | 8.65mm × 6mm | 8.65mm × 3.9mm |

| N (PDIP、14) | 19.3mm × 9.4mm | 19.3mm × 6.35mm | |

| DB (SSOP、14) | 6.2mm × 7.8mm | 6.2mm × 5.3mm | |

| PW (TSSOP、14) | 5mm × 6.4mm | 5mm × 4.4mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 本体サイズ (長さ×幅) は公称値であり、ピンは含まれません。

各ゲートの論理図 (正論理)

各ゲートの論理図 (正論理)