JAJT258 February 2023 DLP6500FLQ , DLP650LNIR , DLP7000 , DLP7000UV , DLP9000X , DLP9000XUV , DLP9500 , DLP9500UV , DLPC410 , DLPC910

3.4 SPI フラッシュのレイアウト接続

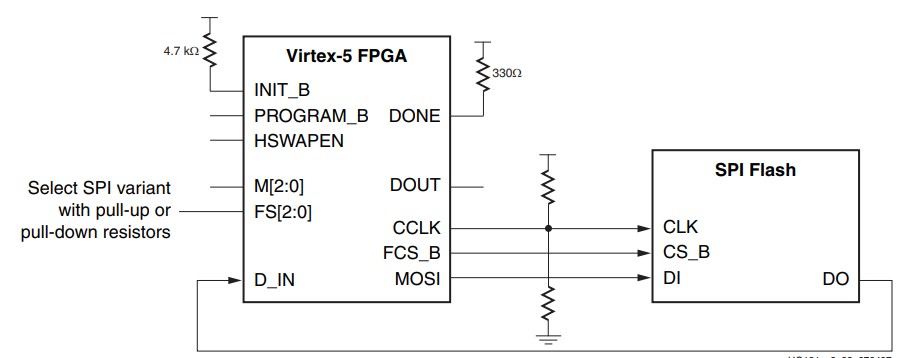

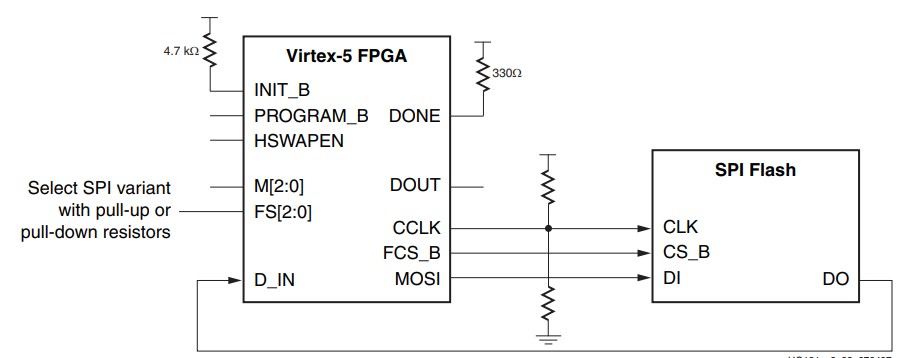

DLPC910 および DLPC410 コントローラは、以下の図に示す接続を使用して SPI フラッシュに接続する必要があります

。

Virtex 5 JTAG インターフェイス経由でプログラミングできるように、SPI フラッシュ書き込み保護 (WP#) を High にプルアップする必要があります。SPI フラッシュが DLPC410 コントローラおよび DLPC910 コントローラとのシリアル通信を一時停止しないように、SPIフラッシュ・リセット (RESET#) またはホールド (HOLD#) を High にプルアップする必要があります。

SPI 構成フラッシュを DLPC410 コントローラおよび DLPC910 コントローラに接続する方法の詳細については、DLPLCRC910EVM および DLPLCRC410EVM の回路図を参照してください。

- FCS_B = DLPC910 コントローラと DLPC410 コントローラのピン AA10

- MOSI = DLPC910 コントローラと DLPC410 コントローラのピン AA9

- CCLK = DLPC910 コントローラと DLPC410 コントローラのピン J10

- D_IN = DLPC910 コントローラと DLPC410 コントローラのピン K11