JAJT260 march 2023

3 アクティブ・クランプ・レッグの設計上の検討事項

PSFB に実装されたアクティブなスナバにより、変圧器の巻線電流は実効デューティ・サイクル (Deff) の期間 (TS) (非ゼロ出力巻線電圧期間) 中に、出力インダクタ電流のように単調増加することはありません。これは、アクティブなスナバのキャパシタ・エネルギーが、入力側からのエネルギー伝達だけに寄与しているのではなく、出力インダクタの活性化にも関与しているためです。入力または変圧器の巻線電流は一般的にピーク電流の検出に利用されているため、入力または変圧器の巻線電流が大きいほど、デューティ・サイクルが大きくなるとは限りません。そのため、非単調な電流のランプ特性により、ピーク電流モード制御が難しくなる可能性があります。

電流が単調増加しているときにピーク電流が検出されるようにするためには、動作電圧と負荷範囲の全体にわたって、DeffTS は、電流・時間バランスが完了する時間 -DCSBTS- よりも常に大きくなるようにする必要があります。PSFB は Deff が大きいほど高効率が期待できるため、一般的に Deff >> DCSB となるような中程度から大きな負荷のかかるときに、Deff がより大きくなるよう設計されています。軽負荷時は、コンバータは、同じ入出力電圧条件下における連続導通モードの Deff よりも小さな Deff になる非連続導通モードで動作します。軽負荷時でも DeffTS が DCSBTS より大きい値を維持できるように、負荷電流に基づいた周波数低減制御を実装しています。

DCSBTS の期間は、ピーク電流モード制御の重要な要素になります。電流・時間バランスが完了するまでどのくらいの時間がかかるかは、重要ですが、答えを出すのが難しい問題です。この問題に答えるには、アクティブ・クランプ・レッグを通る電流を計算する必要があります。

VCL が一定で Lm = ∞ と仮定すると、デューティ・サイクル損失期間 (VSEC = 0 で、iSR1 と iSR2 が代用されている期間) における整流器の電流変化率は、次の 式 2 のように表されます。

ここで、VLr は、Lr にかかる電圧です。

式 3 は、出力インダクタ電流の変化率を計算しています。

式 2 と 式 3 とキルヒホッフの電流法則を使用して、式 4 でアクティブ・クランプ電流の変化率を計算します。

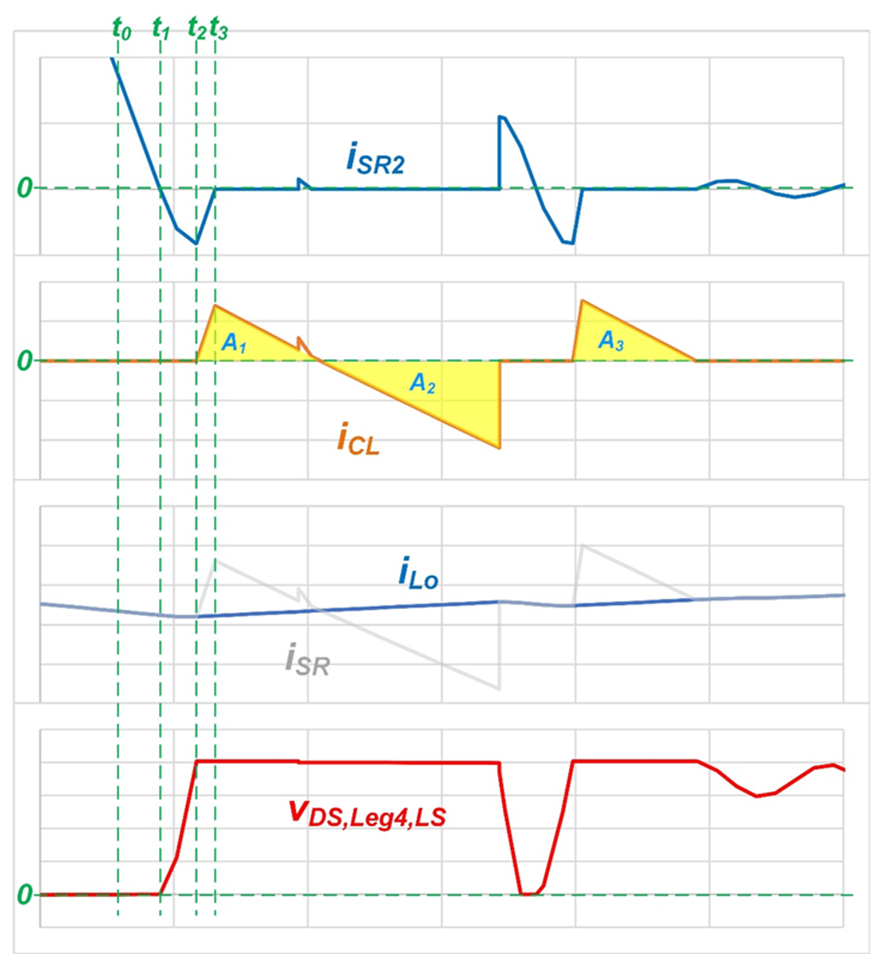

VCL ≈ VIN x NS/NP [3] であるため、ΔiCL を求めるには、式 4 の Δt に合計アクティブ・クランプ・レッグ伝導時間を代入するだけです。ただし、iCL の 2 乗平均平方根値 (RMS) を求めるには、iCL のピーク値が必要です。図 3 に示したように、時間 t2 のときに iSEC = iLo (Coss を VCL に充電した後) となり、かつ時間 t3 (CCL の充電開始時) に iSEC = iSR である場合、iCL,peak は次の 式 5 のように導き出されます。

図 3 アクティブ・クランプ電流の伝導期間前後における主な波形。

図 3 アクティブ・クランプ電流の伝導期間前後における主な波形。時間 t2 における iSR2 の値を求める式は、次の 式 6 のようになります。

t0 から t2 までの iSR2 電流の減少率が同じと仮定すると、t2-t1 間の時間は次の 式 7 から導き出されます。

CL は電流・時間バランスを維持する必要があるため、A1 と A3 の合計面積は A2 と同じ面積になります。

式 7 に示したように、SR Coss はアクティブ・クランプ・レッグのピーク電流を制御しています。低 Coss SR FET を選択すると、アクティブ・クランプ・レッグの RMS 電流は低くなり、その結果、変換効率は向上します。

アクティブなスナバを搭載した PSFB コンバータを設計する際の設計ガイドラインを以下に示します。

- CCL のエネルギーが 1 次側に逆流するのを防ぐため、デューティ・サイクルの損失期間後のみ QCL をオンにする必要があります。

- ボディ・ダイオードが ZVS に電流を伝導している間は、QCL をオンにする必要があります。

- QCL のオン時間が長くなると、SR の電圧ストレスだけでなく VCL も低減しますが、QCL の RMS 電流は増加します。

- SR Coss が低下すると、アクティブ・クランプ・レッグの RMS 電流が低下するだけでなく、SR の電圧ストレスも低減します。

アクティブ・クランプ手法はフルブリッジ整流器だけに限定されるわけではありません。電流ダブラー [4] やセンタータップ付き整流器など、他の種類の整流器にも適用できます。図 4 に、センタータップ付き整流器にアクティブ・クランプを搭載した PSFB コンバータを示します。これは、アクティブ・クランプ・リファレンス設計された 3kW 位相シフトのフル・ブリッジで、270W/in3 以上の電力密度で実装されています。

図 4 センタータップ付き整流器にアクティブ・スナバを搭載した PSFB コンバータ。

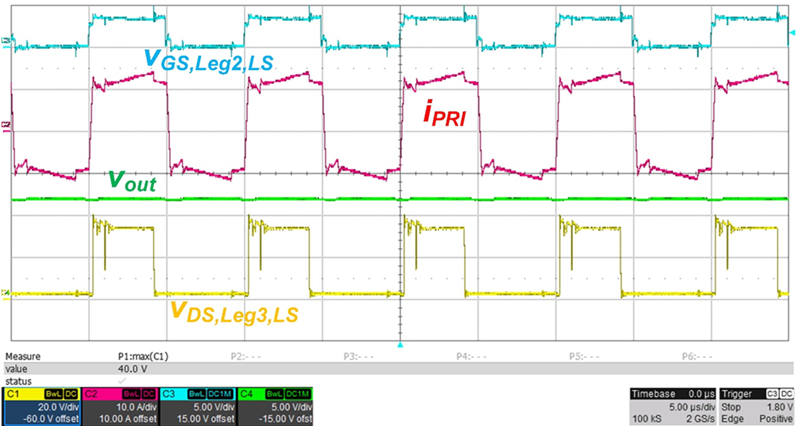

図 4 センタータップ付き整流器にアクティブ・スナバを搭載した PSFB コンバータ。図 5 に示すように、デュアル・アクティブ・クランプ・レッグを使い、負荷電流 250A 時にクランピング損失はほぼない状態 (ごくわずかな導通損失) で、40V の SR 電圧ストレスをクランプすることができます。

図 5 12V/3kW 出力時におけるセンタータップ付き整流器とアクティブ・スナバを搭載した PSFB コンバータの安定状態の波形。

図 5 12V/3kW 出力時におけるセンタータップ付き整流器とアクティブ・スナバを搭載した PSFB コンバータの安定状態の波形。