-

制御の不安定性をもたらす可能性があるファームウェアの誤り JAJT298 February 2024 TMS320F280025C , TMS320F280039C , TMS320F280049C

-

制御の不安定性をもたらす可能性があるファームウェアの誤り

Desheng Guo、Aki Li

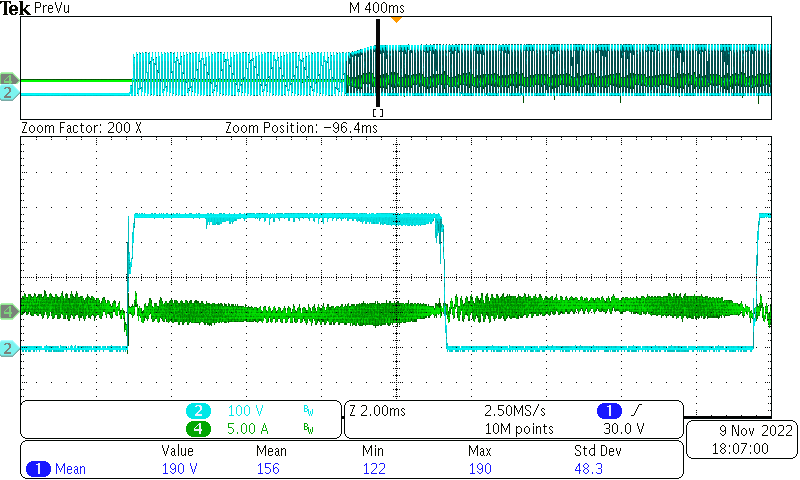

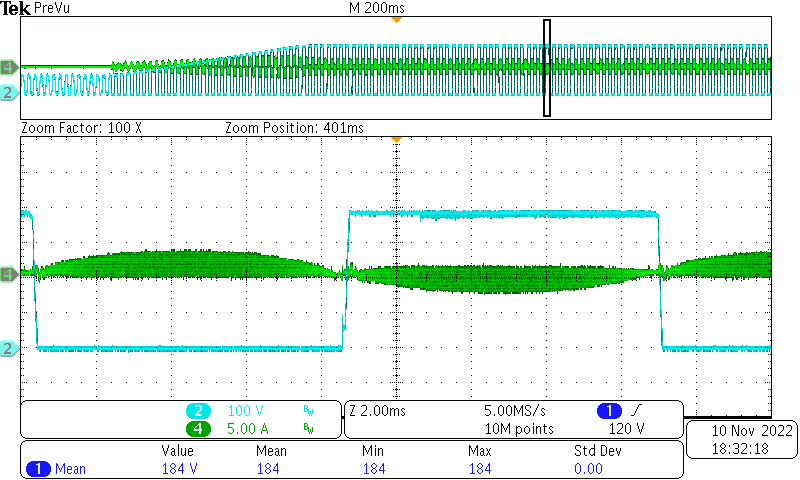

昇圧力率補正 (PFC) などのデジタル電源を設計する際に、図 1 に示すような電流の振動を目にしたことがありますか。

図 1 PFC 段で発生している電流の発振。出典:テキサス・インスツルメンツ

図 1 PFC 段で発生している電流の発振。出典:テキサス・インスツルメンツこの不安定な発振は、制御帯域が広すぎることが原因だとお考えかもしれません。その場合、比例積分 (PI) コントローラの比例ゲイン (Kp) と積分ゲイン (Ki) を小さくし、交差周波数を大幅に低減します。すると、発振は消えます。

しかし、それが最善の解決策でしょうか。電流ループ帯域幅が狭いと、制御速度が低下しますが、全高調波歪 (THD) テストで不合格になることがあります。そして、ソース インピーダンスが少し大きくなると、再び発振が現れることがあります。

この不安定性には他に考えられる原因があるのでしょうか。十分な位相マージンが確保された最善の制御帯域幅を実現するにはどうすればよいでしょうか。デジタル制御ループを詳細に分析し、この潜在的な誤りがどのように発生したかを確認しましょう。また、お使いの制御ファームウェアでこのような不安定性が発生しているかどうかを確認する方法もご説明します。

MCU ベースのデジタル制御

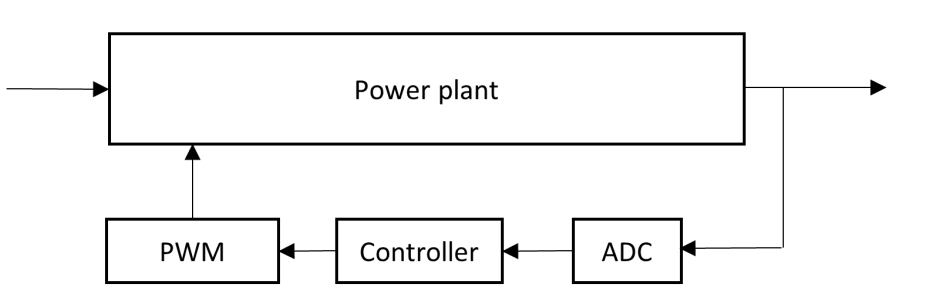

図 2 に、MCU ベースのデジタル制御システムを示します。

図 2 デジタル制御システムは、マイクロコントローラを中心に構成されています。出典:テキサス・インスツルメンツ

図 2 デジタル制御システムは、マイクロコントローラを中心に構成されています。出典:テキサス・インスツルメンツ制御ループは、対象の電流 / 電圧をサンプリングするためのアナログ / デジタル コンバータ (ADC)、調整値を生成するためのデジタル コントローラ、調整を実行するためのパルス幅変調器 (PWM) で構成されており、デューティまたは周波数を変更することで電流 / 電圧の目標値を変更します。

スイッチ モード電源 (SMPS) での ADC サンプリングはしばしば、2 スイッチング サイクルの中間点で行われるため、スイッチングによるノイズを回避できるだけでなく、連続導通モード (CCM) でのパワー インダクタ電流の平均値を取得することもできます。

デジタル コントローラは割り込みサービス ルーチン (ISR) で計算され、PWM 出力と同期してトリガされます。トリガ イベントは PWM の「カウンタ」が「ゼロ」、「周期」、特定の値「CMP」のいずれかと等しくなると発生します。

コントローラがすべての計算を完了した時点で PWM を直ちに更新することは不可能ですが、PWM カウンタが「ゼロ」または「周期」と等しい場合など、特定のタイミングで PWM レジスタにシャドウ レジスタの値をロードする必要があります。カウンタの立ち上がりまたは立ち下がり中に PWM 値が変更された場合、PWM の誤動作、パルスの喪失、パルスの重複が発生する可能性が高くなります。

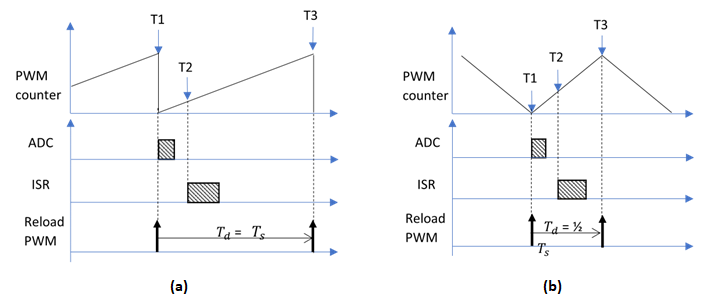

アナログ制御システムとは異なり、デジタル制御はサンプリング周波数によって実行されるため、サンプリングから新しい値が PWM にリロードされるまでの遅延時間 (Td) が必要です。PWM の変更は、PWM 出力が変化する瞬間を調整することで実装されます。この瞬間はシングル エッジ変調 (カウント アップ / カウント ダウン モード) の場合 1 回発生し、デュアル エッジ変調 (カウント アップダウン モード) の場合 2 回発生します。したがって、Td の最小値は、選択した変調リロード周波数に応じて、1 スイッチング サイクル Ts (図 3 の a を参照) または 1/2 スイッチング サイクル Ts/2 (図 3 の b を参照) となります。

図 3 PWM 調整によって最小遅延時間が決まります。(a) アップ モード、(b) アップ ダウン モード。出典:テキサス・インスツルメンツ

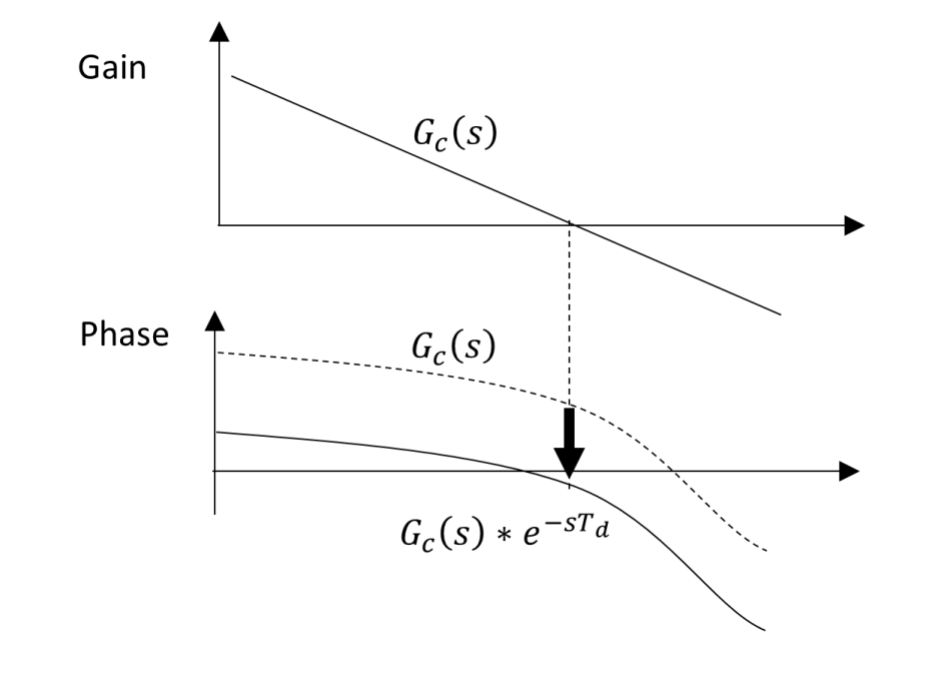

図 3 PWM 調整によって最小遅延時間が決まります。(a) アップ モード、(b) アップ ダウン モード。出典:テキサス・インスツルメンツ図 4 に示すように、Td はその伝達関数で e-sxT d として表されており、位相マージンを減少させます。もちろん、位相マージンが 45 度未満になると、システムは不安定になり、発振が発生します。

図 4 時間遅延の影響を示すボード線図。出典:テキサス・インスツルメンツ

図 4 時間遅延の影響を示すボード線図。出典:テキサス・インスツルメンツデジタル制御の実装で犯しがちなコードの誤り

正しい実行では、Td の最小値は 1 スイッチング サイクル (Ts) の半分のスイッチング サイクル (Ts/2) です。しかし、ADC、ISR、PWM リロードの結果を考慮していない場合、制御遅延を 1 スイッチング サイクルよりも延ばすと、位相マージンが減少し、不安定性につながる可能性があります。

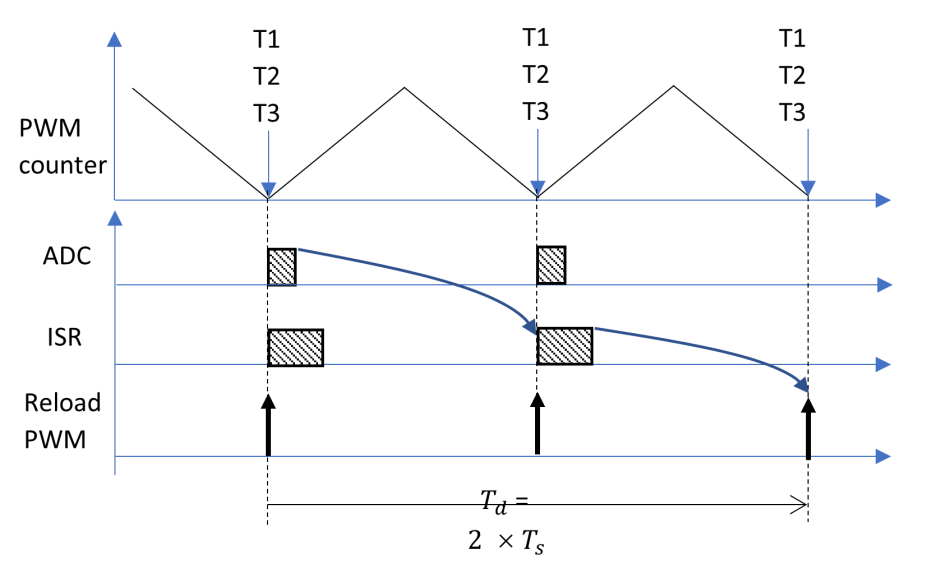

たとえば、図 5 において、ADC の ISR トリガと PWM リロードは、PWM カウンタがゼロになった同じタイミングで開始しています。

すべてのブロックが同時に実行されていますが、ここで Td が 0 になることを期待できるでしょうか。もちろん、そうではないでしょう。

図 5 誤ったコードが原因で遅延時間が長くなる例。出典:テキサス・インスツルメンツ

図 5 誤ったコードが原因で遅延時間が長くなる例。出典:テキサス・インスツルメンツこれは、ADC 変換と ISR 計算の両方が、1 MCU クロック サイクルよりもはるかに長い時間を必要とするためです。ISR が ADC 結果を読み取った時点で、ADC 変換はまだ完了していません。したがって、ISR は計算のために「古い」サンプル値を取得し、最新の値の計算は次のスイッチング サイクルまで先延ばしにされます。ISR の計算が完了すると、新しい PWM 値はシャドウ レジスタのみに書き込まれ、その値は次のスイッチング サイクルでリロードされます。実際には、Td の総制御遅延は 2 スイッチング サイクル (2 × Ts) になります。

ここに示した例のほかにも、その他の実装で同様に制御遅延が延びる場合があります。たとえば、ISR コードの中でコントローラの計算の後に ADC 値の読み取りを配置した場合、コントローラの計算の前に N サイクル アルゴリズム平均を追加した場合などです。

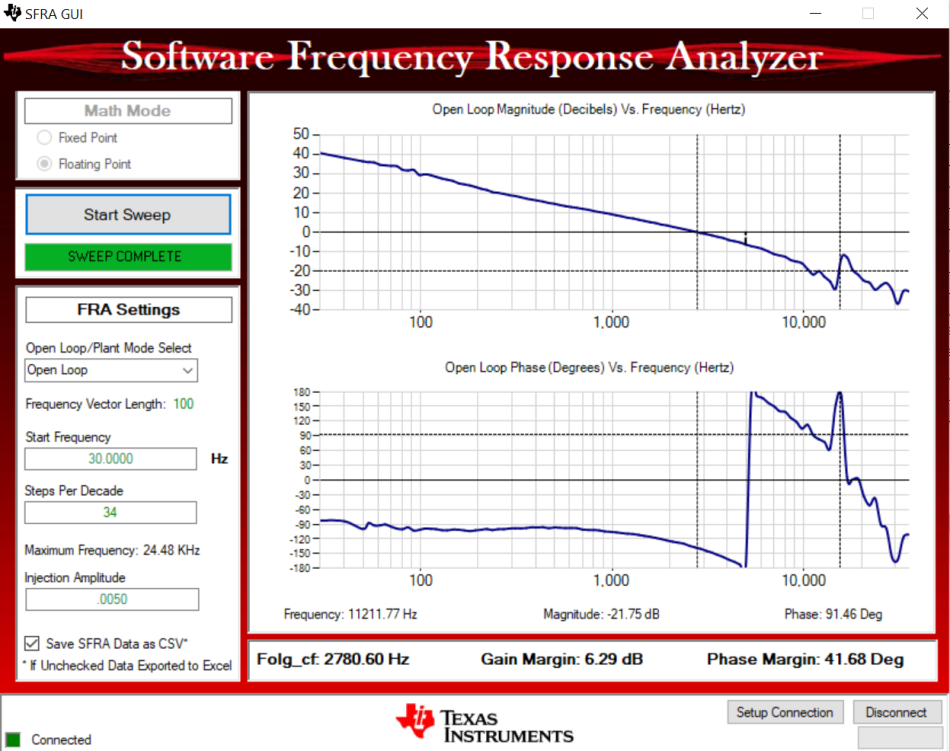

図 6 に示すように、図 5 の誤った実装を使用してゲイン交差周波数を約 3kHz に設定した場合、位相マージンは 41.68 度になります。これは 45 度未満であり、チョーク電流に大きな発振 (図 1 の波形を参照) が現れるため、交差周波数を 2kHz 未満に下げる必要があります。すると今度は iTHD が悪化し、要件を満たさなくなります。

図 6 誤ったコード実装によるボード線図。出典:テキサス・インスツルメンツ

図 6 誤ったコード実装によるボード線図。出典:テキサス・インスツルメンツ設計ソリューション

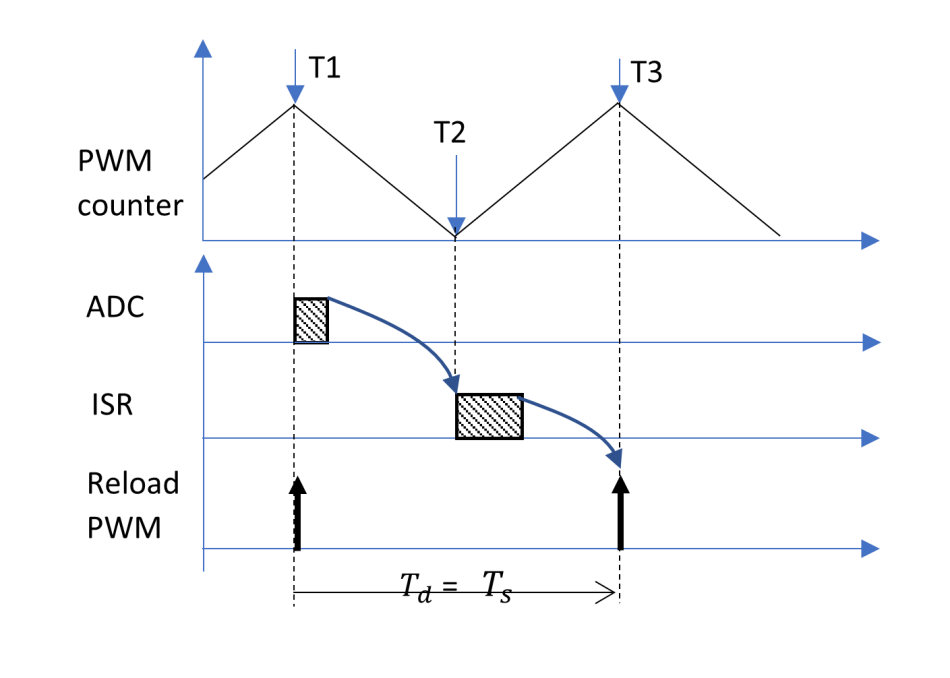

この問題は、「カウンタが周期と等しくなる瞬間」に ADC 変換を移動し、次の「カウンタが周期と等しくなる瞬間」に PWM をリロードすることで、簡単に解決できます (図 7 を参照)。

図 7 コードの改善による制御遅延の短縮。出典:テキサス・インスツルメンツ

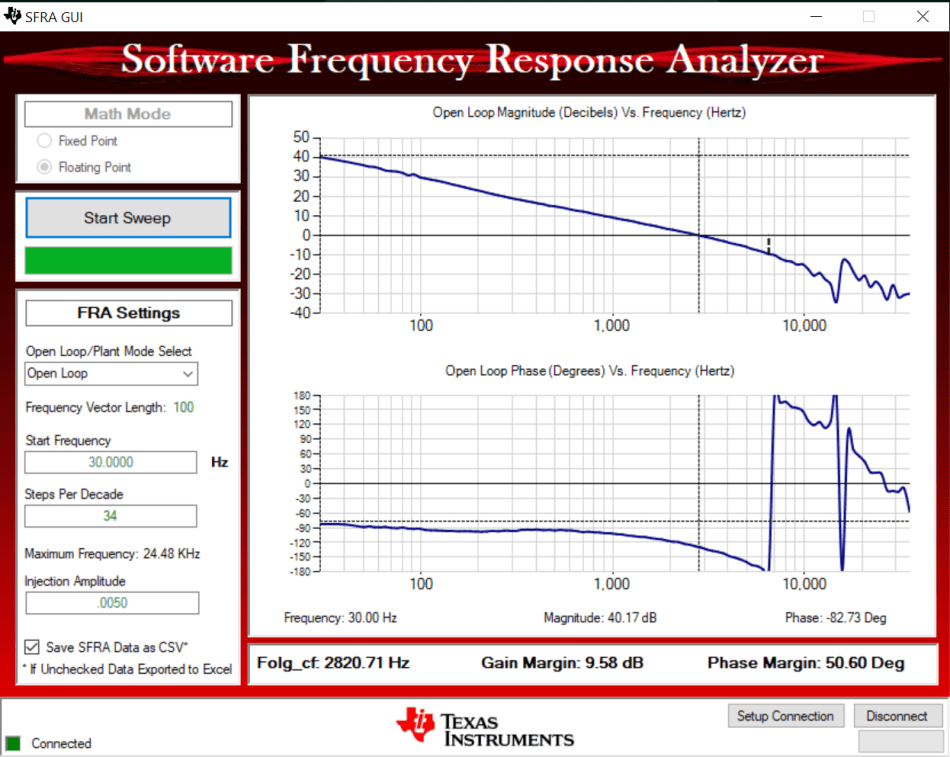

図 7 コードの改善による制御遅延の短縮。出典:テキサス・インスツルメンツ制御遅延は 1 スイッチング サイクルに短縮されます。図 8 と図 9 に示すように、位相マージンは大幅に増加し、電流の発振はなくなります。

図 8 改善されたコードによるボード線図。出典:テキサス・インスツルメンツ

図 8 改善されたコードによるボード線図。出典:テキサス・インスツルメンツ 図 9 改善されたコードによる波形。出典:テキサス・インスツルメンツ

図 9 改善されたコードによる波形。出典:テキサス・インスツルメンツ適切に構成された制御方式

デジタル実装での制御遅延 (ADC サンプリングから PWM 調整まで) は、位相マージンを減少させ、発振の原因となります。この問題に取り組む際には、ADC のサンプリング、コントローラの計算、PWM のリロードの結果を考慮してください。適切に構成された制御方式では、遅延を半分 (1 スイッチング サイクル) に最小化できるため、位相マージンとループ帯域幅が増加しています。

重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。IMPORTANT NOTICE

Copyright © 2024, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社