JAJU732E June 2019 – April 2024 TMS320F28P550SJ , TMS320F28P559SJ-Q1

4.1.2.4 高分解能の位相シフト構成

使用する高分解能機能:

- 高分解能の位相シフト

- 高分解能のデッド バンド

- 高分解能デューティ → 利用不可、CTMODEB は 1 に設定

- 高分解能周期 → 利用不可、CTMODEB は 1 に設定

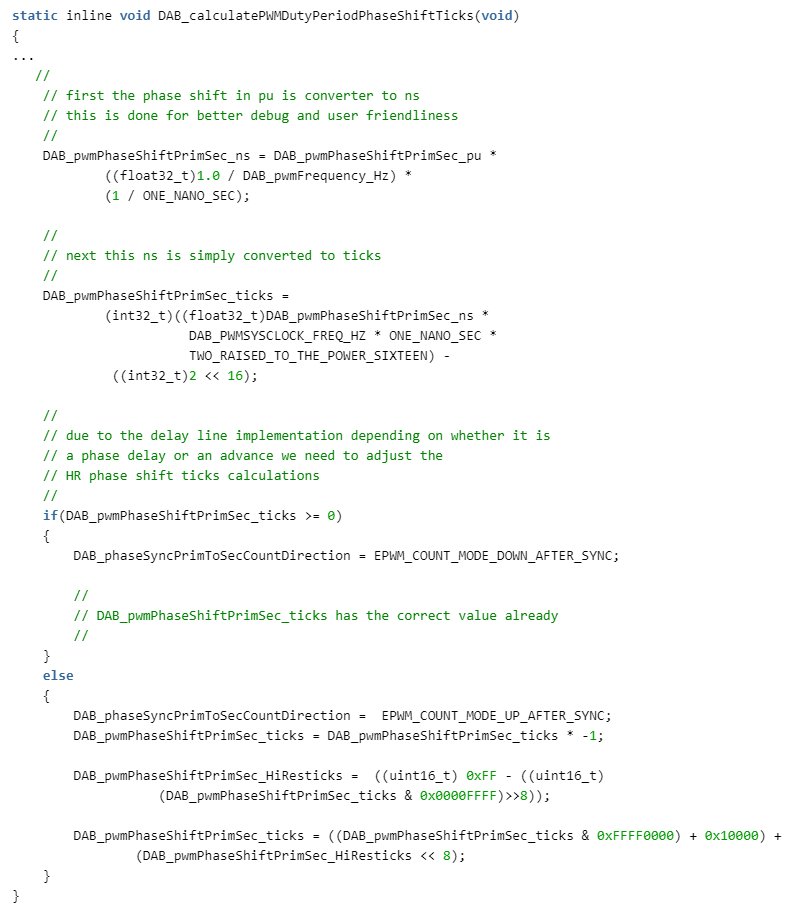

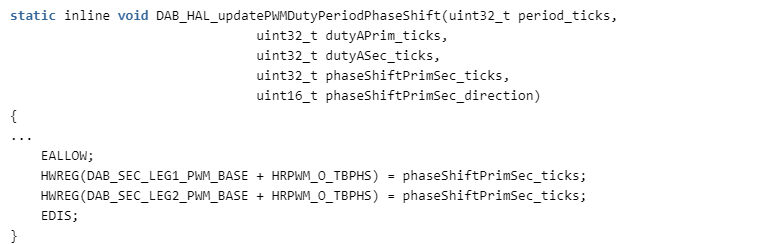

2 次側の PWM パルスは、1 次側の PWM パルスに対して位相シフトされます。位相シフトを制御することにより、1 次側から 2 次側へ、またはその逆方向に電力を伝送できます。伝送される最大電力は、デュアル アクティブ ブリッジでの位相シフトの値に大きく影響されます。小型の直列インダクタであれば、小さい位相シフトで最大の電力伝達を実現できる可能性があります。位相シフトの変化する範囲が小さいので、正確に制御するためには、位相を細かいステップで増減させる必要があります。位相制御は、F28004x の高分解能機能を使用して実装されています。ISR1 内の関数 DAB_calculatePWMDutyPeriodPhaseShiftTicks() は、電圧と電流の両方のモード制御に必要な高分解能位相制御を計算します。これにより、 急激な負荷の変化に対して、電流波形に大きなオーバーシュートや過渡を生じることなく、スムーズに対応できます。

図 4-3 PWM 機能 1

図 4-4 PWM 機能 2

変数 DAB_phaseSyncPrimToSecCountDirection が更新され、電力フローの順方向モードまたは逆方向モードを制御します。

図 4-5 PWM の構成