JAJU732E June 2019 – April 2024 TMS320F28P550SJ , TMS320F28P559SJ-Q1

4.1.2.3 PWM の構成

デュアル アクティブ ブリッジの 1 次側レグと 2 次側レグの PWM を生成するために、アップダウン カウント モードを使用します。高分解能 PWM を使用する場合、PRIM_LEG1_H PWM パルスは周期イベントの中心に配置され、タイム ベースはアップダウン カウントに構成されます。その後、相補型スイッチ用に、高分解能デッドタイムを持つ相補型パルスが生成されます。LEG1 と LEG2 の間には、フルブリッジ動作のために 180 度の位相シフトがあります。これは、PWM モジュールの機能を使用して xA 出力と xB 出力を入れ替えることで実現します。このアプリケーションのスイッチング周波数は 100kHz です。アップ ダウン カウント モードでは、TBPRD レジスタの値は 500 に設定されます。

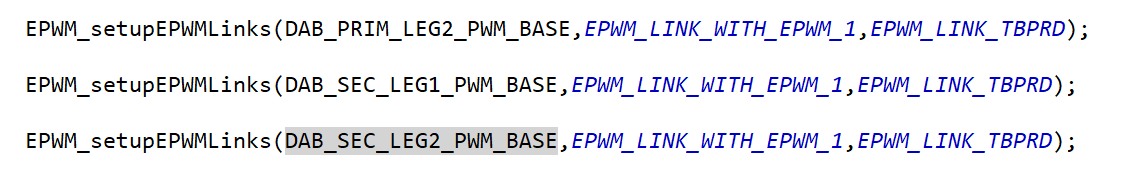

デューティ サイクル値は EPWM ベースの CMPA レジスタに読み込まれ、50% のデューティ サイクルを生成するように構成されます。アクション クオリファイア モジュールは、比較イベントで PWM 出力を制御するために必要なアクションを出力します。タイプ 4 PWM のグローバル リンク メカニズムは、レジスタの更新に必要なサイクル数を減らし、高周波動作を可能にするために使用されます。たとえば、関数 DAB_HAL_setupPWM() 内の以下のコードは、すべての PWM レグの TBPRD レジスタをリンクしています。

このリンクを使用すると、PRIM_LEG1 TBPRD レジスタへの書き込みを 1 回行うだけで、PRIM_LEG2、SEC_LEG1、SEC_LEG2 に値が書き込まれます。

図 4-2 PWM 書き込み