JAJU732E June 2019 – April 2024 TMS320F28P550SJ , TMS320F28P559SJ-Q1

3.7.1 構成

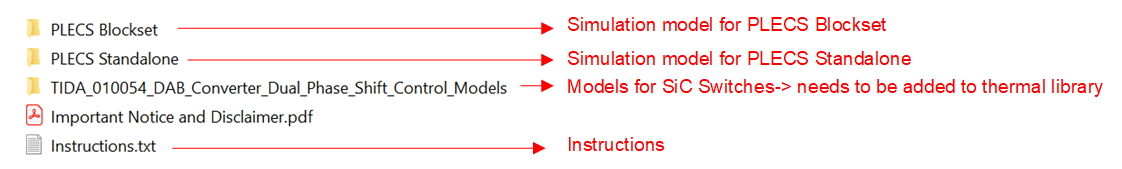

図 3-14 に、ダウンロード可能なファイルのフォルダ構造を示します。

図 3-14 PLECS シミュレーション - フォルダ概要

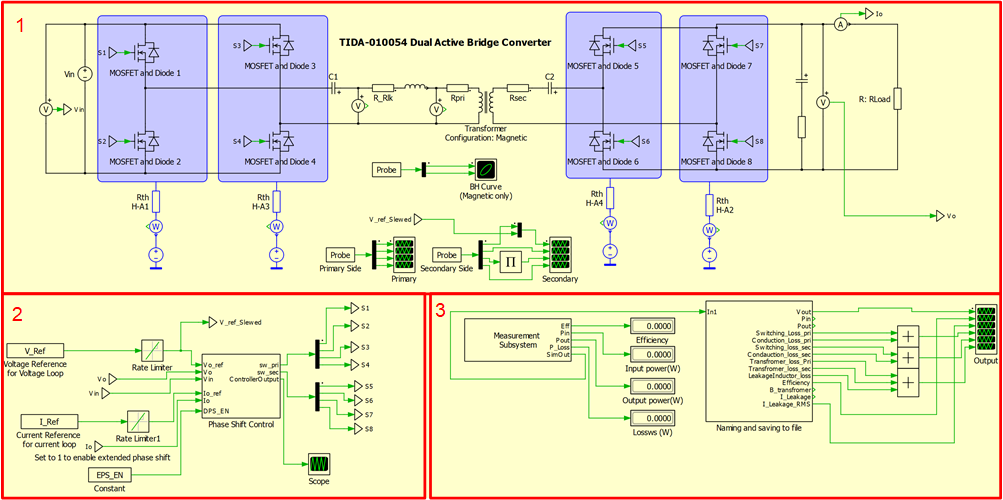

図 3-14 PLECS シミュレーション - フォルダ概要図 3-15 に PLECS シミュレーション デッキを示します。

図 3-15 PLECS シミュレーション デッキ

図 3-15 PLECS シミュレーション デッキPLECS シミュレーション デッキは、3 つの主要部分で構成されています。

- パワー コンバータ:

- パワー コンバータを備えており、メーカーの SiC-FET (シリコン カーバイド電界効果トランジスタ) モデルを搭載

- ヒートシンク (熱解析のためのセットアップは TIDA-010054 と同様)

- スイッチ ノードの波形を分析する 1 次側スコープ

- 出力電圧、電流、電力を分析する 2 次側スコープ

- トランスの磁気挙動を分析するための BH 曲線

- 位相シフト制御:

- 電圧および電流ループ用コントローラを備えています。位相シフト制御ブロックを開いて、コントローラの構成を変更することで、電圧ループと電流ループを切り替えることができます。

- 拡張位相シフト変調は、初期化スクリプトで EPS_EN = 1 を設定することによりイネーブルできます。

- 測定サブシステム:

- システム内での損失を測定して合計し、効率を計算

- 入力電力を確認するための表示。シミュレーション実行中の出力電力効率と損失

- ファイル ブロックへの命名と保存、測定サブシステムからの信号の命名、Microsoft® Excel® ファイルへの保存 (スタンドアロン バージョンのみ)