JAJU751G September 2019 – October 2023

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1システムの説明

-

2システム概要

- 2.1 ブロック図

- 2.2 設計上の考慮事項

- 2.3

主な使用製品

- 2.3.1 LMG3422R050 — ドライバと保護機能を内蔵した 600V GaN

- 2.3.2 TMCS1100 — 高精度絶縁型電流センス・モニタ

- 2.3.3 UCC27524 — デュアル、5A、高速 2 次側パワー MOSFET ドライバ

- 2.3.4 UCC27714 — 620V、1.8A、2.8A 1 次側 / 2 次側ゲート・ドライバ

- 2.3.5 ISO7721 — 高速、堅牢な EMC 特性、強化絶縁型、基本デュアル・チャネル・デジタル・アイソレータ

- 2.3.6 ISO7740 および ISO7720 — 高速、低消費電力、堅牢な EMC デジタル・アイソレータ

- 2.3.7 OPA237 — 単一電源オペアンプ

- 2.3.8 INAx180 — 2 次側および 1 次側電圧出力、電流センス・アンプ

- 2.3.9 TPS560430 — SIMPLE SWITCHER 4V~36V、600mA、同期整流降圧コンバータ

- 2.3.10 TLV713 — ポータブル機器向けフォールドバック電流制限付き 150mA 低ドロップアウト (LDO) レギュレータ

- 2.3.11 TMP61 — 温度検出向けシリコン・ベース小型リニア・サーミスタ

- 2.3.12 CSD18510Q5B — 40V、N チャネル NexFET MOSFET、シングル SON5x6、0.96mΩ

- 2.3.13 UCC28911 — 定電圧、定電流、1 次側レギュレーション付き 700V フライバック・スイッチャ

- 2.3.14 SN74LVC1G3157DRYR — 単極双投アナログ・スイッチ

- 2.4 システム設計理論

-

3ハードウェア、ソフトウェア、テスト要件、テスト結果

- 3.1

必要なハードウェアとソフトウェア

- 3.1.1 ハードウェア

- 3.1.2 PFC 段ソフトウェア

- 3.1.3 LLC 段ソフトウェア

- 3.1.4 PFC + LLC 段のデュアル・テスト

- 3.1.5 ライブ・ファームウェア・アップデートの概要

- 3.2 テストと結果

- 3.1

必要なハードウェアとソフトウェア

- 4設計ファイル

- 5ソフトウェア・ファイル

- 6関連資料

- 7著者について

- 8改訂履歴

- 132

3.1.3.5.2.4 コードの実行

- ツールバーの <F8> キーまたは [Run] ボタン (

) を使用して、コードを実行します。

) を使用して、コードを実行します。 - 12V 出力では 10A の負荷を使用します。

- DC 380V 電源を設定します。電源電流制限を、このテストに適したレベルに設定します。次に、この 380V 電源をオンにします。

- この時点では、コンバータの Start コマンドが開始されていないため、出力電圧は引き続きゼロになるはずです。

- 次に、[Expressions] ウィンドウで、LLC_startFlag を 1 に設定します。

- コンバータの動作が開始され、出力は約 12V に上昇するはずです。注: 出力電圧が約 12V まで上昇しない場合は、すぐに DC 380V 電源をオフにします。セクション 3.1.3.5.1 に示すように、最初にラボ 1 の動作を確認します。また、この基板を再度テストする前に、基板の部品を再検証し、ハードウェアの問題 (部品表 (BOM) と一致しない部品や PCB の製造上の問題など) をデバッグする必要が生じることがあります。

- 負荷を変化させたときの出力電圧および入力電流への影響を観測します。実質的に出力電圧には影響はありません。同様に、入力電圧を変化させたときの影響を観測します。ここでも、実質的に出力電圧には影響はありません。

- PWM ゲート駆動信号、入力電圧、電流および出力電圧など、さまざまな波形をオシロスコープでプローブすることもできます。この絶縁型 DC/DC コンバータでこれらの高電圧と大電流をプローブする際には、適切な安全上の注意を払い、適切な接地要件を考慮する必要があります。

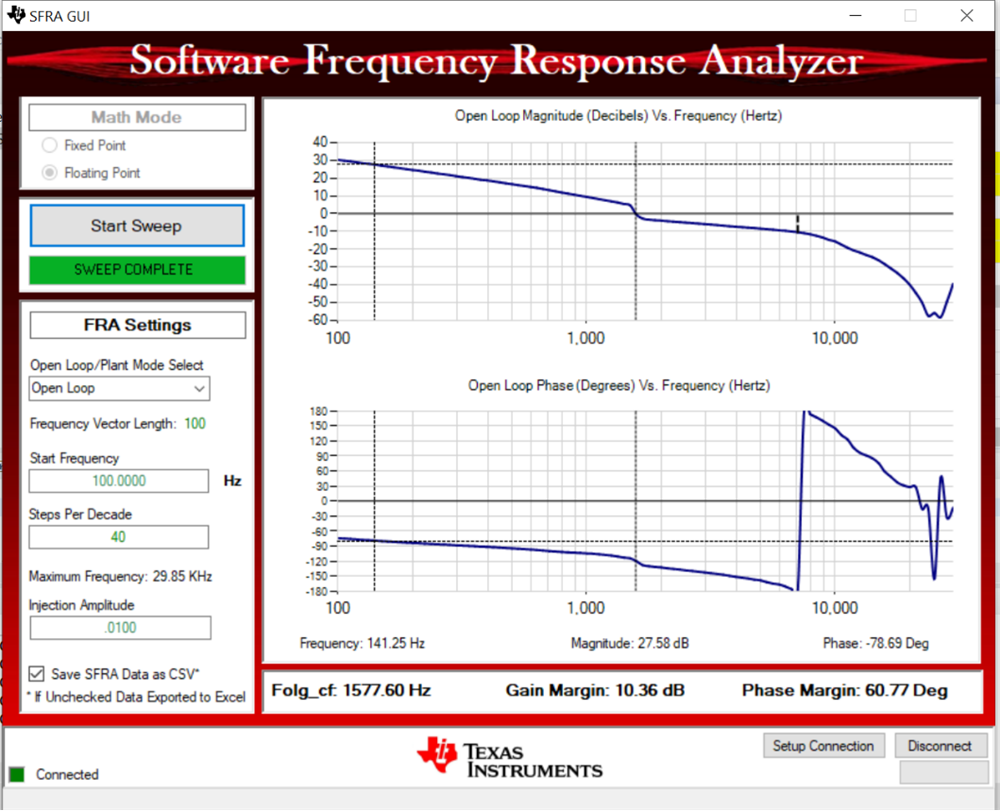

- main.syscfg ファイルを選択し、SFRA を開きます。[Setup Connection] をクリックし、適切な COM ポートを選択します。ボーレートが 57600 に設定されており、[Boot on Connect] がオフになっていることを確認します。 [OK] ボタンをクリックします。 [Floating Point] 演算を選択します。 SFRA GUI で [Connect] をクリックします。 GUI を接続したら、[Start Sweep] をクリックします。 SFRA はさまざまな周波数の適用を開始し、周波数解析の応答を収集します。

図 3-30 SFRA 実行、LLC 閉ループ、開ループ・ゲイン

図 3-30 SFRA 実行、LLC 閉ループ、開ループ・ゲイン - DC 380V 電源をオフにします。

- リアルタイム・モードのマイコンを完全に停止するには、2 段階の手順を踏みます。まず、ツールバーの [Halt] ボタン (

) を使用するか [Target] → [Halt] の順にクリックしてプロセッサを停止します。 次に、

) を使用するか [Target] → [Halt] の順にクリックしてプロセッサを停止します。 次に、 をクリックしてマイコンをリアルタイム・モードから解除します。最後に、

をクリックしてマイコンをリアルタイム・モードから解除します。最後に、 をクリックしてマイコンをリセットします。

をクリックしてマイコンをリセットします。 - [Terminate Debug Session] ([Target] → [Terminate all])

をクリックして、CCS デバッグ・セッションを終了します。

をクリックして、CCS デバッグ・セッションを終了します。