JAJU825C december 2022 – june 2023

3.3 ソフトウェア

表 3-3 はソフトウェア・フローの詳細を示します。

表 3-3 ソフトウェア・フローとタイミング

| STEP | 時間 (μs) | 備考 |

|---|---|---|

| 基板の初期化 | 2929 | 電源投入後 1 回 |

| SP + ADC 電圧セトリングを閉じる | 500 | スイッチ SP を閉じる時間と ADC 入力の電圧が安定するまでの遅延時間 500μs。容量性負荷に応じて、この時間を調整する必要があります (セクション 1.2 を参照)。 |

| Viso,P および VDC,P を測定する | 126 | ノイズを最小化するため、両方の電圧はインターリーブおよび平均化の 20 倍の値で測定されます |

| SP を開き SN を閉じる | 400 | 開始 SP と終了 SN の間に 400μs の遅延が実装されています。 |

| ADC の電圧セトリング | 500 | ADC 入力の電圧が安定するまでの遅延は 500μs。容量性負荷に応じて、この時間を調整する必要があります (セクション 1.2 を参照)。 |

| Viso,N および VDC,N を測定する | 126 | ノイズを最小化するため、両方の電圧はインターリーブおよび平均化の 20 倍の値で測定されます |

| Riso,P および Riso,N を計算する | 13 | Riso,P および Riso,N の最終計算 |

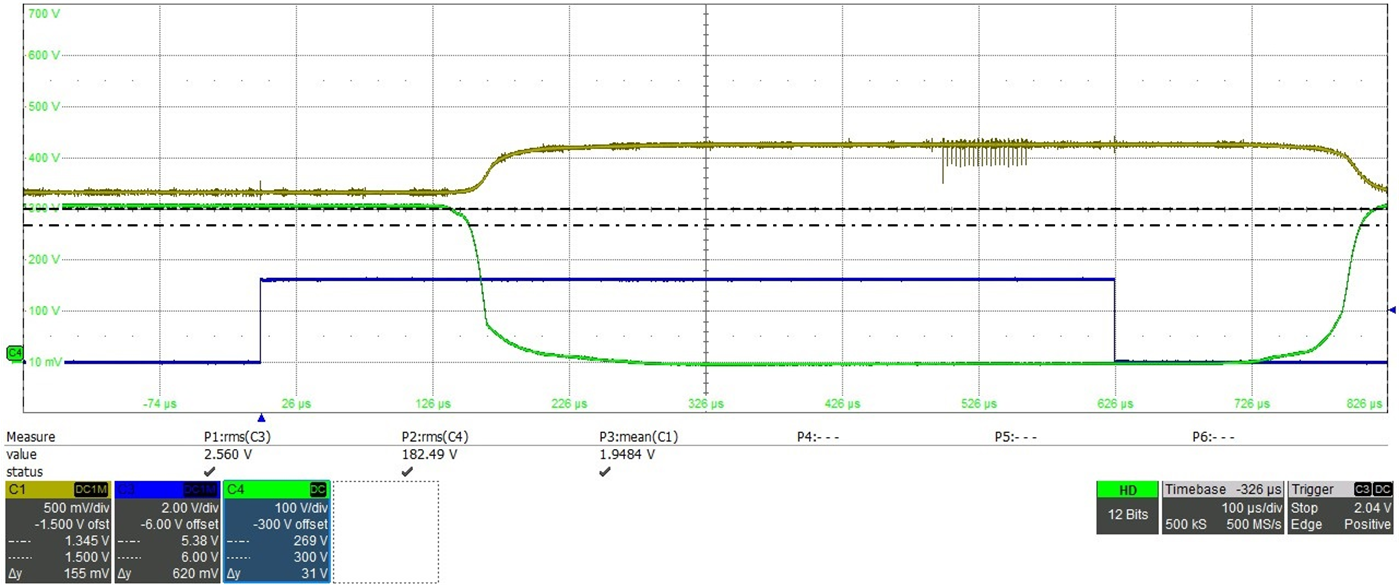

ソフトウェアの初期化には約 3ms を要し、電源投入後に 1 回完了する必要があります。その後の絶縁抵抗の測定には、それぞれ 1.7ms を要します。この高速測定時間は、従来のリレーと比較して、TPSI2140 を使用して測定パスでスイッチングを行う場合の大きな利点の 1 つです。TPIS2140 のスイッチング動作と ADC 入力での電圧セトリングを図 3-1 に示します。

青:イネーブル信号、緑:TPSI2140 の両端間の電圧、黄:ADC 入力での電圧

図 3-1 TPSI2140 のスイッチング動作と ADC 入力電圧