JAJU869 January 2024

2.3.2 FPGA DDR2 SDRAM インターフェイスの配線

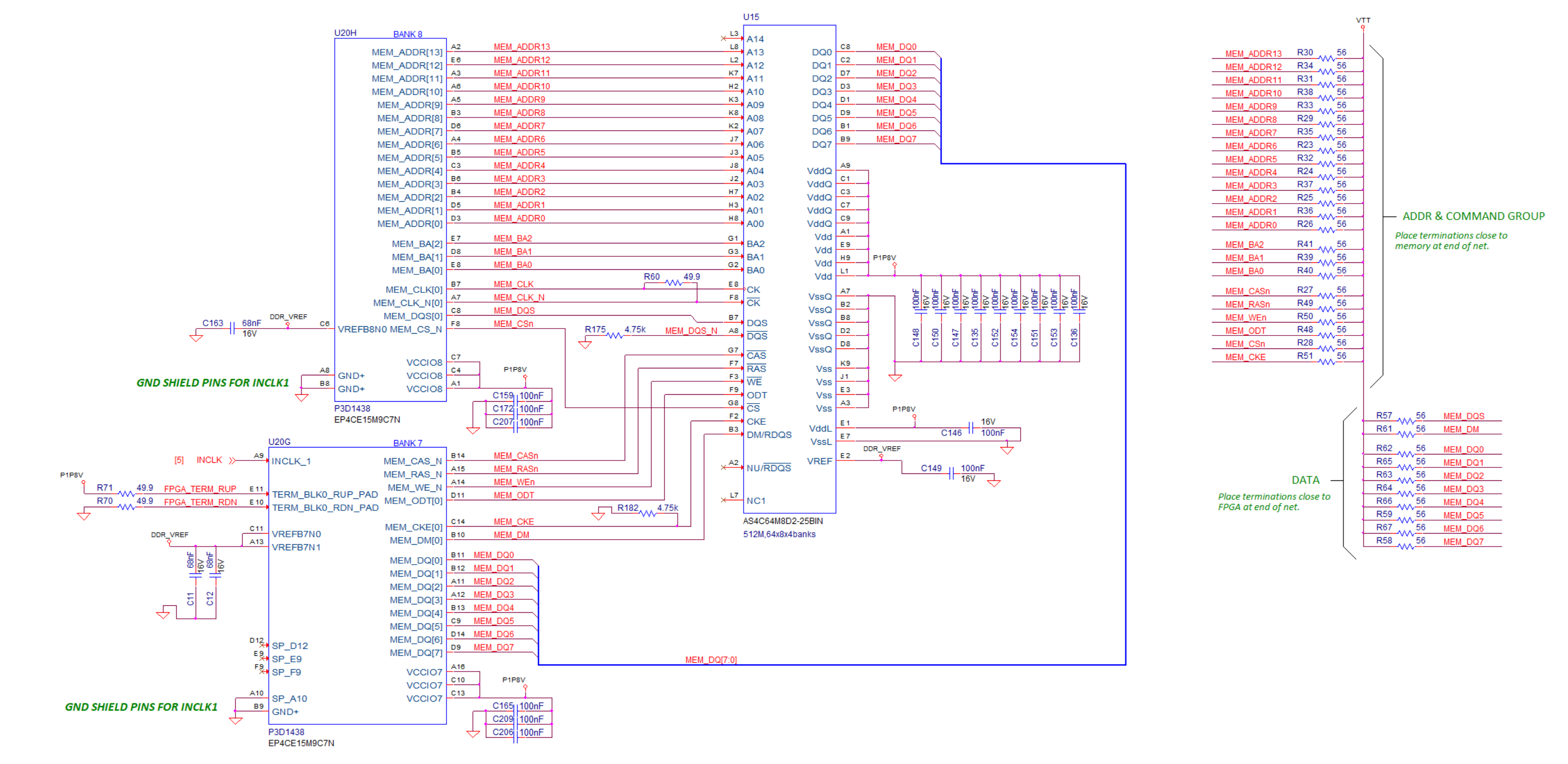

FPGA から DDR2 SDRAM へのインターフェイスは、400MHz DDR クロック レートに基づいています。Intel® Cyclone® IV E FPGA (EP4CE15M9C7N) からアライアンス DDR2 SDRAM (AS4C64M8D2-25BIN) へのインターフェイス図を図 2-3 に示し、推奨インターフェイス レイアウト ガイドラインを表 2-5 に定義しています。

図 2-3 FPGA-DDR2 インターフェイス

図 2-3 FPGA-DDR2 インターフェイス表 2-5 推奨する FPGA-DDR2 PCB マッチングおよびパターンの遅延

| グループ | グループ名 | グループ内の長さの一致 | 他の信号に対する長さの一致 | その他のルーティング要件 |

|---|---|---|---|---|

| MEM_ADDR[13:0]、MEM_BA[2:0]、MEM_CASn、MEM_RASn、MEM_WEn、MEM_ODT MEM_CKE、MEM_CSn | アドレス / 管理グループ | グループ内 ±50ps | MEM_CLK および MEM_CLK_N より 0ps~15ps 小さい | 50Ω - DDR2 パターン端に終端を配置 - 最大長 250ps - 最小長 200ps |

| MEM_DQ[7:0]、MEM_DM、MEM_DQS | データ グループ | グループ内 ±10ps | MEM_CLK、MEM_CLK_N ±10ps | 50Ω - 内部レイヤを使用 - 同じレイヤで配線 - FPGA パターン端に終端を配置 - 最大長 250ps - 最小長 200ps |

| MEM_CLK、MEM_CLK_N | CLK グループ | グループ内 ±2ps | MEM_DQS ±2ps は、ADDR および CNTL グループよりも 0ps~15ps 長い値である必要があります | 100 差動 - 外部レイヤのパターンを最小化 - 内部レイヤを使用 - 最大長 250ps - 最小長 200ps |

PCB 配線の最良事例:

- 可能な場合は、PCB の内部レイヤを使用

- DDR_DQ(7:0)、MEM_DM、DDR_DQS を同じレイヤに配線