JAJU878 November 2022 ADS117L11 , ADS127L11

- 概要

- リソース

- 特長

- アプリケーション

- 5

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing, and Test Results

- 5Design and Documentation Support

- 6About the Author

4.4.1 Noise Floor and Dynamic Range

The excitation current circuit and booster stage are not powered for the noise floor and dynamic range tests.

Begin by setting the ADC input MUX to offset test mode.

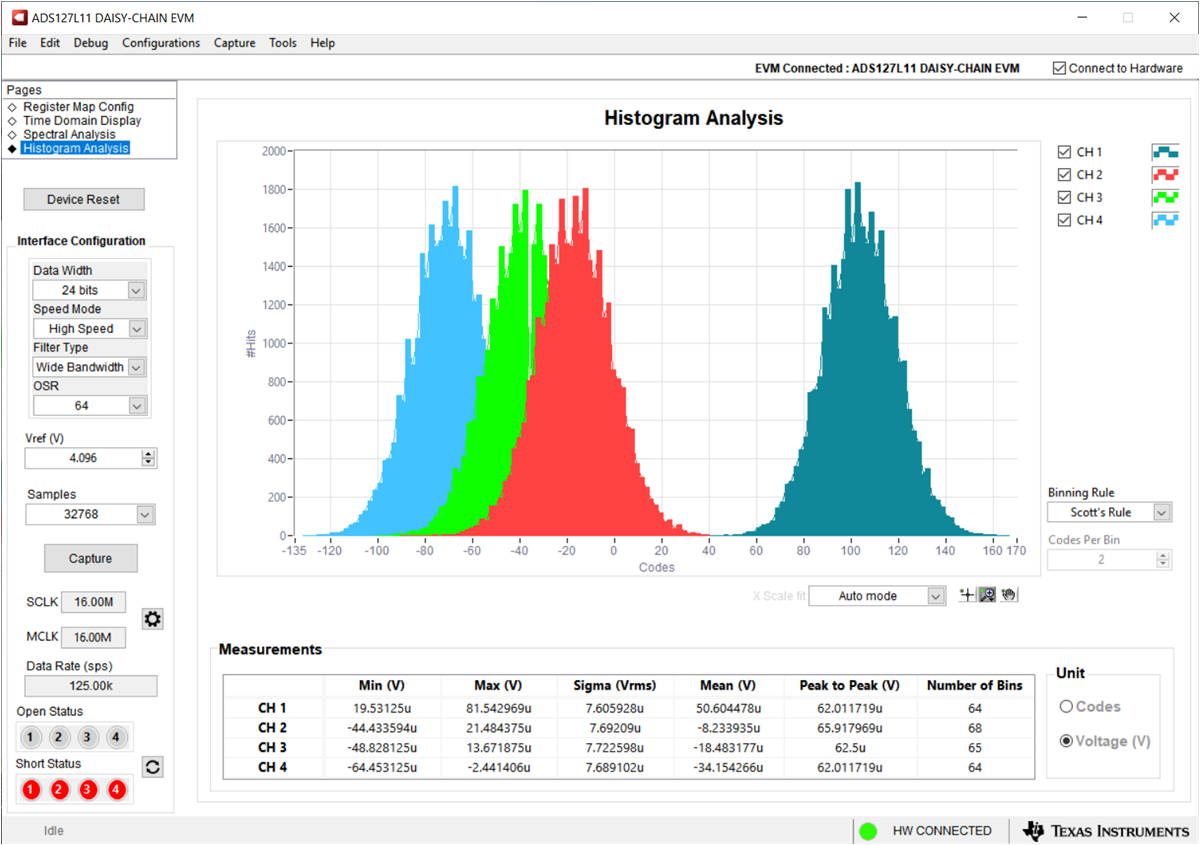

Figure 4-9 Histogram Plot of ADCs Inputs

Shorted (Test Mode)

Figure 4-9 Histogram Plot of ADCs Inputs

Shorted (Test Mode)The ADC intrinsic voltage noise sigma is 7.7 μV, and offset of about 50 μV which is in line with the values in the ADS127L11 400-kSPS, Wide-Bandwidth, 24-Bit, Delta-Sigma ADC data sheet.

Next, short the front-end input (J8A, 2-3 = short).

Figure 4-10 Histogram Plot of Front-End

Inputs Shorted

Figure 4-10 Histogram Plot of Front-End

Inputs ShortedThe full front-end voltage noise is around 19.8 μV, which is equivalent to 103 dB of Dynamic Range. The frequency plot in Figure 4-11 shows a clean spectrum with the highest tone at 94 dBFS.

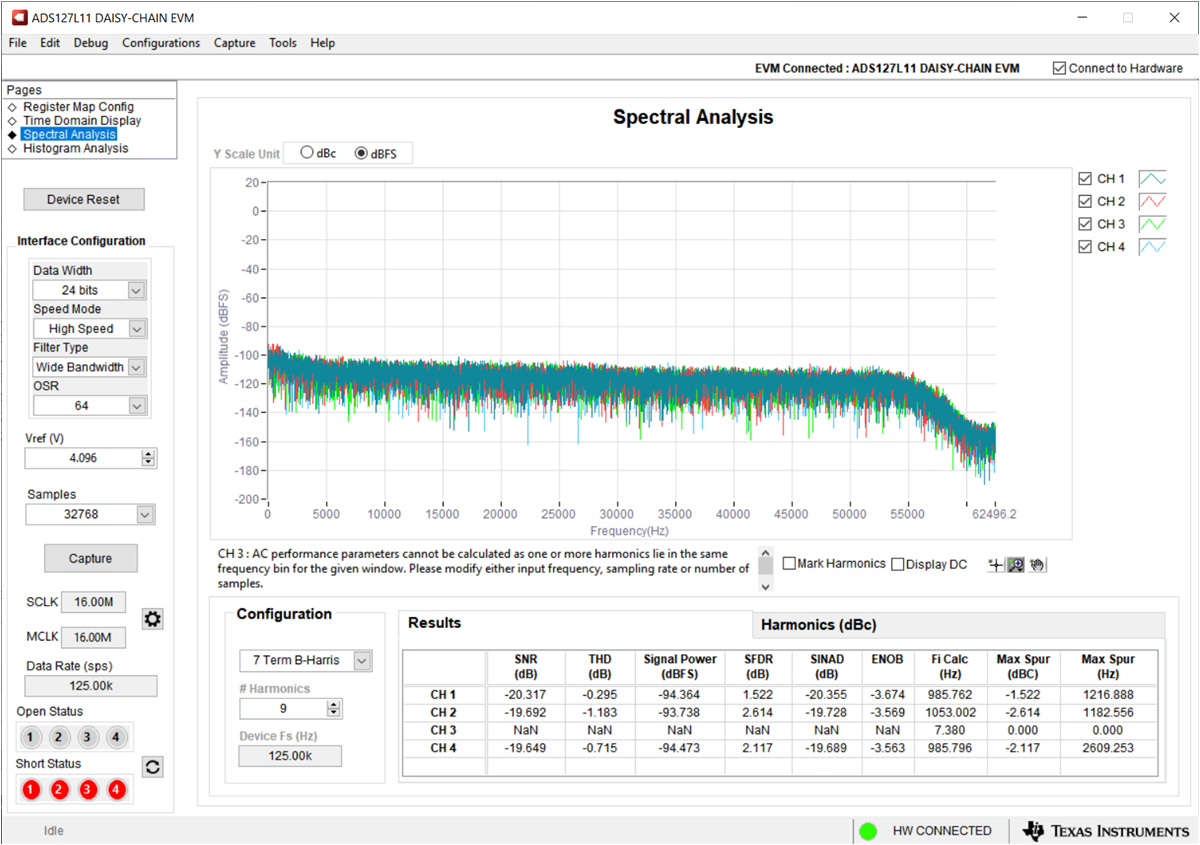

Figure 4-11 Frequency-Domain Plot of

Front-End Inputs Shorted

Figure 4-11 Frequency-Domain Plot of

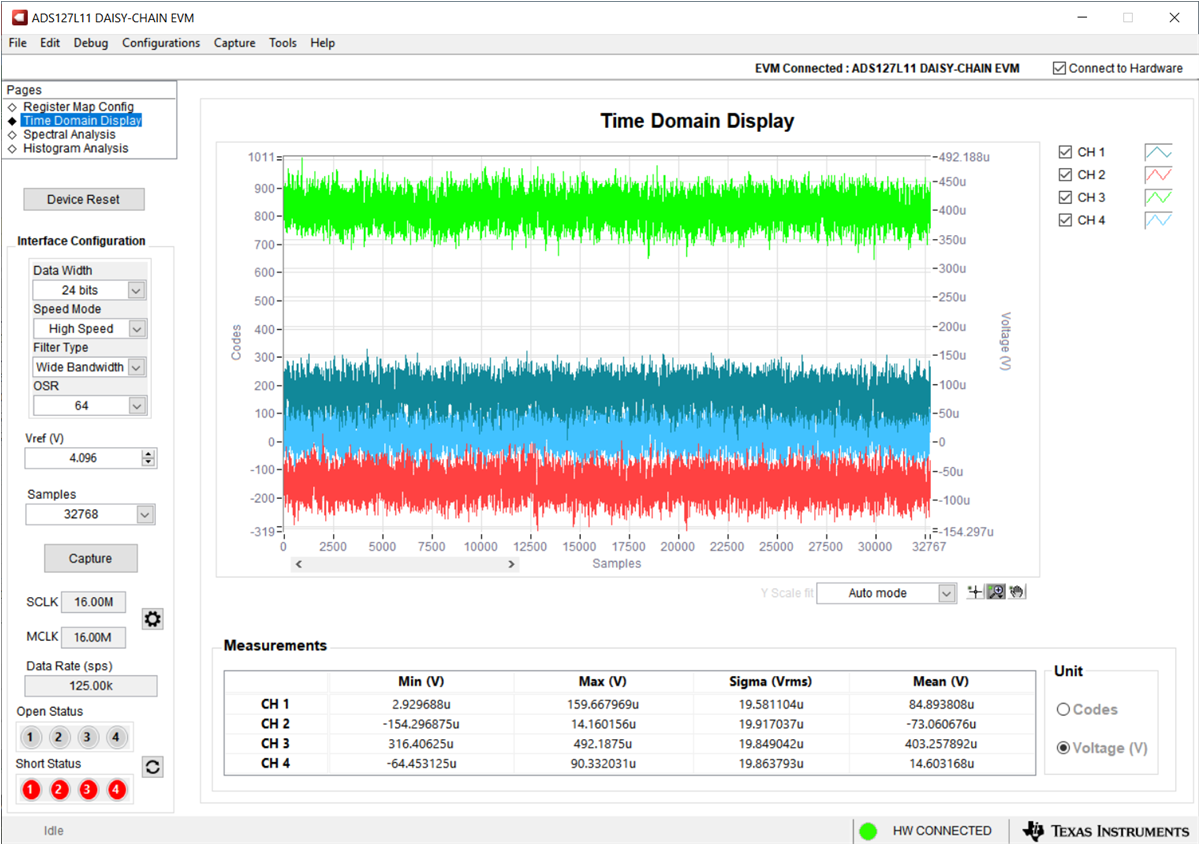

Front-End Inputs ShortedThe time-domain plot (see Figure 4-12) verifies that there are no visible tones. The mean value of the channels are well below 0.5 mV which is the estimated offset of the whole channel including the offsets of OPA2320 (with gain of 4) and THS4551 (with gain of 2), and the ADS127L11 offset.

Figure 4-12 Time-Domain Plot of Front-End

Inputs Shorted

Figure 4-12 Time-Domain Plot of Front-End

Inputs Shorted