JAJU880A December 2022 – December 2024

3.4.3 補助電源とシステム消費電流

補助電源方式に起因して、このデザインはシャットダウン モードでの消費電流が非常に小さいです。スタック アーキテクチャにより、システム全体の消費電流は、最上位スタックからの出力電流とバッテリ負極ポートに戻る電流の最大値となります。電流値は、10Ω の抵抗の両端の電圧から測定できます。

さらに、このデザインでは、2 つのスタック グループ間の消費電流のギャップが最適化され、グループ間での追加的なセル バランシングが回避されます。消費電流のギャップは、Icell32 から IGND を差し引くことで計算できます。図 3-8 に消費電流のテスト設定を示し、表 3-3 に平均システム消費電流と平均グループ不均衡電流のテスト結果を示します。

図 3-8 消費電流のテスト設定

図 3-8 消費電流のテスト設定| 説明 | Icell32 | Icell16 | IGND | 電流のギャップ (μA) | 合計電流 (μA) | |

|---|---|---|---|---|---|---|

| 通常モード (MOSFET オフ) | 電流 (μA) | 4550 | 550 | 4565 | 15 | 4565 |

| 通常モード (MOSFET オン) | 電流 (μA) | 4504 | 550 | 4484 | 20 | 4504 |

| シップ モード | 電流 (μA) | 7 | 0 | 7 | 0 | 7 |

このデータは、低電圧 ESS 用の電源レール構成でテストされています。別の構成では、バッテリではなく外部の 24V で電力供給されるためです。電流テストには、INA229_239EVM と 10Ω の抵抗を使用しています。通常モードでは、充電 MOSFET と放電 MOSFET がオンまたはオフのいずれかの状態でも、総消費電流は 4.6mA 未満です。グループ間の不均衡は 20μA 未満です。出荷モードでの消費電流は 10μA 未満です。

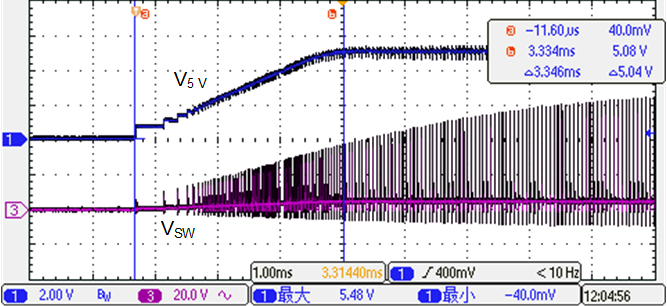

図 3-9 に、補助電源のスタートアップ時のテスト結果を示します。

図 3-9 DC/DC のスタートアップ

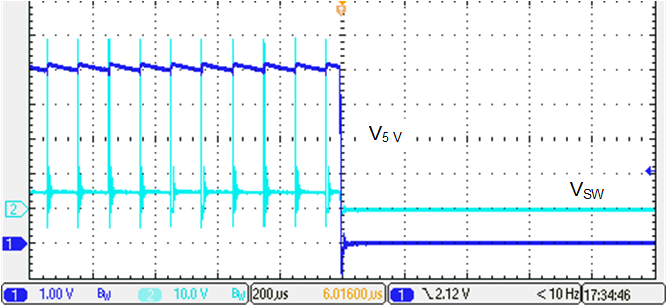

図 3-9 DC/DC のスタートアップこのデザインでは、DC/DC 出力が短絡した場合のフォルトも考慮しています。図 3-10 に、DC/DC の短絡テスト結果を示します。出力が短絡した場合、熱の問題を防止するため、MCU によって DC/DC は無効化されます。

図 3-10 DC/DC 出力の短絡

図 3-10 DC/DC 出力の短絡