JAJU904A October 2023 – June 2024

3.3.2 TCD_PHYL_INTF_UARTTRANSDELAY

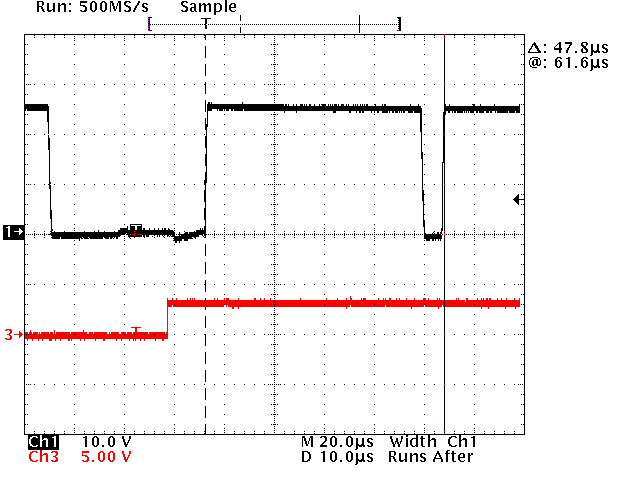

t2 時間を判定するには、CQ ライン上の UART フレームの立ち上がりエッジを観測し、あるフレームから次のフレームまでの時間を測定します。その後、11 ビットの送信時間が減算され、2 フレーム間の時間のみが残るようになります。この時間は、ビット時間の 0 ~ 3 倍にすることができます。COM3 の場合、最大 13µs が許容されます。

黒 = C/Q ライン、赤 = TIOL112 イネーブル信号

図 3-19 T2 測定、最初のデバイスの応答スタート ビットから 2 番目のスタート ビットへの遷移式 1. 47.8µs – 11 × 4.34µs = 0.06µs, this equals 0.01 TBIT

UART 送信バッファはダイレクト メモリ アクセス (DMA) 経由で自動的にリロードされるため、t2 時間は非常に短いと予想されます。測定は、測定の時間分解能によって制限されます。