JAJU904A October 2023 – June 2024

3.3.3 TCD_PHYL_INTF_RESPONSETIME

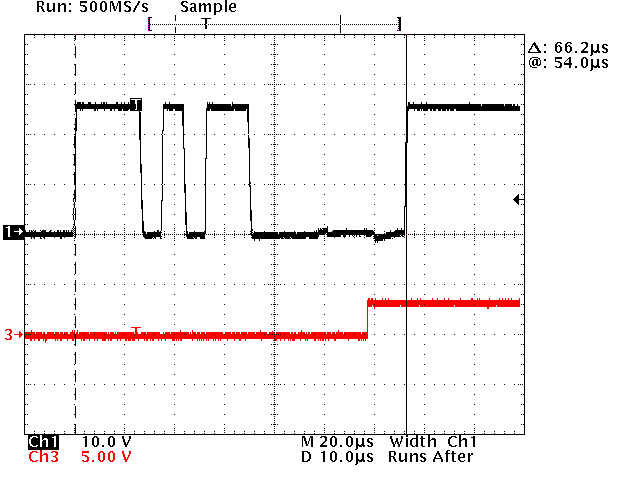

TA を測定するには、最後のマスタ メッセージの開始ビットから、デバイスからの応答の開始ビットまでの時間を測定します。マスターからの最後のメッセージの時刻が減算されます。この時間は、ビット時間の 1 ~ 10 倍にすることができます。COM3 では、これにより 4.34µs と 43.4µs が可能になります。

黒 = C/Q ライン、赤 = TIOL112 イネーブル信号

図 3-20 TA 測定、マスタ スタート ビットからデバイス スタート ビットへの遷移式 2. 66.2µs – 11 × 4.34µs = 18.46µs, this equals 4.25 TBIT

測定時間が制限範囲内にあります。