JAJU922A October 2022 – February 2024

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1 CLLLC システムの説明

- 2 CLLLC システムの概要

- 3 トーテムポール PFC システムの説明

- 4 主な使用製品

-

5 ハードウェア、ソフトウェア、試験要件、試験結果

- 5.1 必要なハードウェアとソフトウェア

- 5.2

テストと結果

- 5.2.1 テストのセットアップ (初期設定)

- 5.2.2

CLLLC のテスト手順

- 5.2.2.1 ラボ 1.1 次側から 2 次側への電力フロー、PWM ドライバの開ループ チェック

- 5.2.2.2 ラボ 2.1 次側から 2 次側への電力フロー、PWM ドライバおよび保護付き ADC の開ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.3 ラボ 3.1 次側から 2 次側への電力フロー、閉電圧ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.4 ラボ 4.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.5 ラボ 5.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側で抵抗性負荷が電圧源と並列に接続されてバッテリ接続をエミュレートしている状態)

- 5.2.3 TTPLPFC のテスト手順

- 5.2.4 テスト結果

- 6 デザイン ファイル

- 7 ソフトウェア ファイル

- 8 関連資料

- 9 用語

- 10著者について

- 11改訂履歴

5.2.2.2.4 コードの実行

をクリックしてプロジェクトを実行します。

をクリックしてプロジェクトを実行します。- ここで、CLLLC_clearTrip 変数に 1 を書き込んで検出をクリアします。

- Watch ビューで、CLLLC_vPrimSensed_Volts、CLLLC_iPrimSensed_Amps、CLLLC_vSecSensed_Volts、CLLLC_iSecSensed_Amps の各変数が定期的に更新されているかどうかチェックします。(注:この時点では電力が印加されていないため、これらの値はゼロに近くなっています。)

- 入力 VPRIM DC 電圧を 0V から 400V に徐々に上げます。CLLLC_vPrimSensed_Volts に正しい値が表示されていることを確認します。

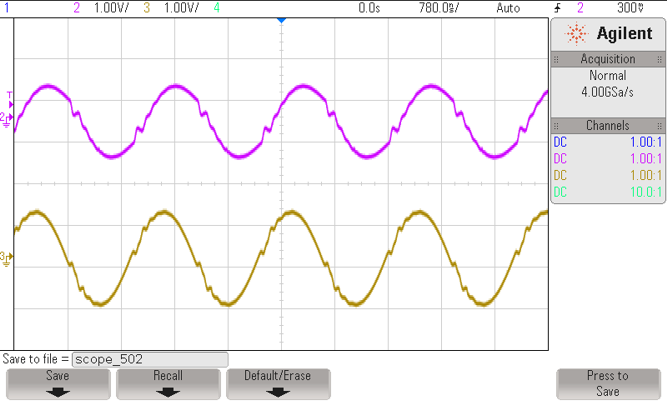

- デフォルトでは CLLLC_pwmPeriodRef_pu 変数は、図 5-10 に示すように 0.599 に設定されており、これは 500.8kHz です。これは、コンバータの直列共振周波数に近いですが、実際のハードウェアに搭載されている部品のばらつきが原因で、直列共振周波数より低くなったり、高くなったりします。たとえば、図 5-11 では、直列共振周波数よりもわずかに低い周波数が確認できます。

- VSEC 変数は、設計したタンク ゲインに応じて、300V 近い電圧を示します。CLLLC_vSecSensed_Volts が正しい電圧を示していることを確認します。これにより、基板の電圧センシングが検証されます。

![TIDM-02013 ラボ 2 [Expression] ウィンドウ、共振時 TIDM-02013 ラボ 2 [Expression] ウィンドウ、共振時](/ods/images/JAJU922A/GUID-4866A40F-96E5-4075-AB95-5B2C33A65E16-low.png) 図 5-10 ラボ 2 [Expression] ウィンドウ、共振時

図 5-10 ラボ 2 [Expression] ウィンドウ、共振時- テスト条件で指定された負荷では、PRIM 側と SEC 側からの電流は、CLLLC_iPrimSensed_Amps で 4.8A、CLLLC_iSecSensed_Amps で 6.8A になります。

図 5-11 ラボ 2、共振時の 1 次側 (ch2) 電流と 2 次側 (ch3) 電流

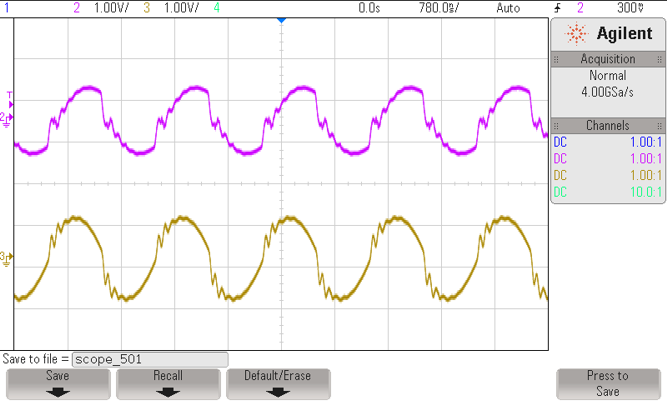

図 5-11 ラボ 2、共振時の 1 次側 (ch2) 電流と 2 次側 (ch3) 電流- 次に、さまざまな周波数 (共振より高い周波数、共振より低い周波数) での動作を確認するには、CLLLC_pwmPeriodRef_pu 変数を 639kHz の周波数に対応する 0.47 に変更します。この条件での波形を 図 5-12 に示します。

図 5-12 ラボ 2、直列共振周波数を上回る 1 次側 (ch2) 電流と 2 次側 (ch3) 電流

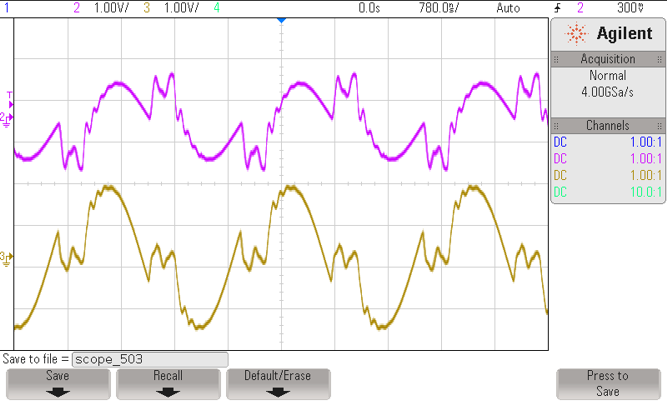

図 5-12 ラボ 2、直列共振周波数を上回る 1 次側 (ch2) 電流と 2 次側 (ch3) 電流- 次に、CLLLC_pwmPeriodRef_pu に 0.8 を入力して、直列共振周波数を下回る状態で動作をテストします。これにより、生成周波数は 374kHz になります。この場合、1 次側電流は不連続になり、2 次側のデューティ サイクルが変調して、図 5-13 に示すダイオード エミュレーションが実現されます。

- これにより、基本的なレベルで PWM ドライバとハードウェアの接続を検証できます。

図 5-13 ラボ 2、直列共振周波数を下回る 1 次側 (ch2) 電流と 2 次側 (ch3) 電流

図 5-13 ラボ 2、直列共振周波数を下回る 1 次側 (ch2) 電流と 2 次側 (ch3) 電流