JAJU922A October 2022 – February 2024

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1 CLLLC システムの説明

- 2 CLLLC システムの概要

- 3 トーテムポール PFC システムの説明

- 4 主な使用製品

-

5 ハードウェア、ソフトウェア、試験要件、試験結果

- 5.1 必要なハードウェアとソフトウェア

- 5.2

テストと結果

- 5.2.1 テストのセットアップ (初期設定)

- 5.2.2

CLLLC のテスト手順

- 5.2.2.1 ラボ 1.1 次側から 2 次側への電力フロー、PWM ドライバの開ループ チェック

- 5.2.2.2 ラボ 2.1 次側から 2 次側への電力フロー、PWM ドライバおよび保護付き ADC の開ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.3 ラボ 3.1 次側から 2 次側への電力フロー、閉電圧ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.4 ラボ 4.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.5 ラボ 5.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側で抵抗性負荷が電圧源と並列に接続されてバッテリ接続をエミュレートしている状態)

- 5.2.3 TTPLPFC のテスト手順

- 5.2.4 テスト結果

- 6 デザイン ファイル

- 7 ソフトウェア ファイル

- 8 関連資料

- 9 用語

- 10著者について

- 11改訂履歴

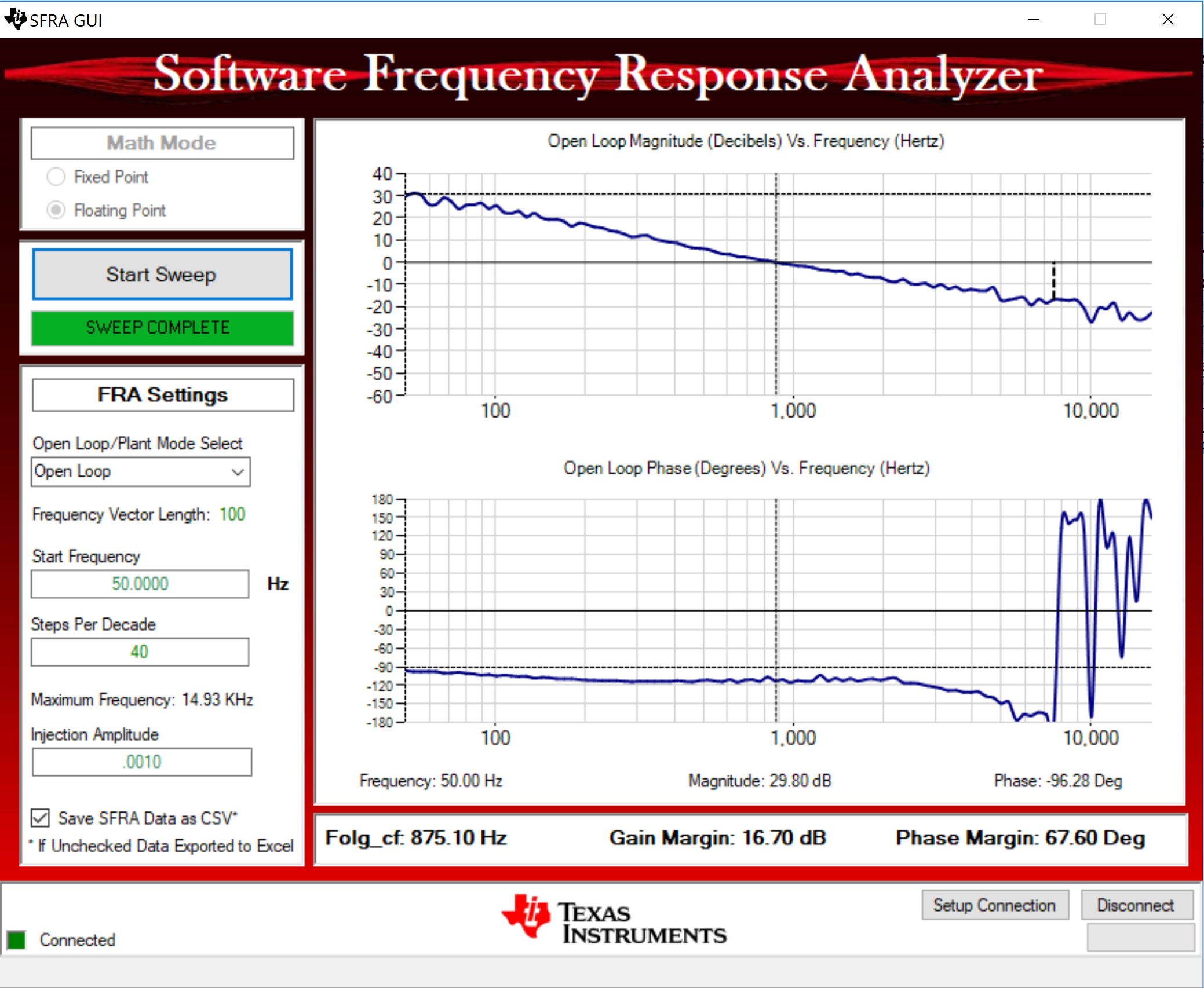

5.2.2.3.4 閉電圧ループに対する SFRA の測定

- このビルドのソフトウェアには SFRA が統合されているため、ハードウェアを測定して、設計した補償器が十分なゲイン マージンと位相マージンを提供していることを検証できます。SFRA を実行するには、プロジェクトを実行したまま、<Install directory >\C2000Ware_DigitalPower_SDK_<version>\libraries\sfra\gui\SFRA_GUI.exe に移動します。

- SFRA GUI でデバイスのオプションを選択します。たとえば、F280039 の場合は浮動小数点を選択します。[Setup Connection] をクリックします。ポップアップ ウィンドウで [Boot on Connect] オプションを選択解除し、適切な COM ポートを選択します。[OK] をクリックします。SFRA GUI に戻り、[Connect] をクリックします。

- SFRA GUI がデバイスに接続します。これで [Start Sweep] をクリックして、SFRA 掃引を開始できるようになりました。 SFRA 掃引が完了するまでには数分かかります。SFRA GUI のプログレス バーを確認したり、UART の動作を示す制御カード裏面の青色 LED の点滅をチェックすることで、動作を監視できます。終了すると、図 5-22 のように開ループ プロットによるグラフが表示されます。

図 5-22 閉電圧ループに対する SFRA 開ループ プロット (Vprim 400V、Vsec 300V、電力 1.972kW、出力に抵抗性負荷あり)

図 5-22 閉電圧ループに対する SFRA 開ループ プロット (Vprim 400V、Vsec 300V、電力 1.972kW、出力に抵抗性負荷あり)また、周波数応答データは SFRA データ フォルダ下のプロジェクト フォルダに保存され、SFRA 実行時のタイム スタンプが記録されます。

このデータは設計した補償器とほぼ一致していますが、開ループでの測定は、小信号の導入によってコンバータの DC ポイントがドリフトする可能性があり、それによって誤差の影響を受けやすいため、偏差が生じるのは当然のことです。

さまざまな電圧で SFRA をテストし、システムが動作可能な範囲全体で安定していることを確認します。

- これにより、電圧ループの設計を検証できます。

- システムを安全に停止させるには、入力 VPRIM 電圧をゼロまで下げます。[Watch] ウィンドウの電圧と電流がゼロに下がるのを観測します。

- リアルタイム モードのマイクロコントローラを完全に停止するには、2 段階の手順を踏みます。まず、ツールバーの [Halt] ボタン (

) を使用するか、[Target] → [Halt] の順にクリックして、プロセッサを停止します。次に、

) を使用するか、[Target] → [Halt] の順にクリックして、プロセッサを停止します。次に、 をクリックして、マイクロコントローラをリアルタイム モードから解除します。最後に、マイクロコントローラ (

をクリックして、マイクロコントローラをリアルタイム モードから解除します。最後に、マイクロコントローラ ( ) をリセットします。

) をリセットします。 - [Terminate Debug Session] (

) ([Target] → [Terminate all]) をクリックして、CCS デバッグセッションを終了します。

) ([Target] → [Terminate all]) をクリックして、CCS デバッグセッションを終了します。