JAJU922A October 2022 – February 2024

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1 CLLLC システムの説明

- 2 CLLLC システムの概要

- 3 トーテムポール PFC システムの説明

- 4 主な使用製品

-

5 ハードウェア、ソフトウェア、試験要件、試験結果

- 5.1 必要なハードウェアとソフトウェア

- 5.2

テストと結果

- 5.2.1 テストのセットアップ (初期設定)

- 5.2.2

CLLLC のテスト手順

- 5.2.2.1 ラボ 1.1 次側から 2 次側への電力フロー、PWM ドライバの開ループ チェック

- 5.2.2.2 ラボ 2.1 次側から 2 次側への電力フロー、PWM ドライバおよび保護付き ADC の開ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.3 ラボ 3.1 次側から 2 次側への電力フロー、閉電圧ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.4 ラボ 4.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.5 ラボ 5.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側で抵抗性負荷が電圧源と並列に接続されてバッテリ接続をエミュレートしている状態)

- 5.2.3 TTPLPFC のテスト手順

- 5.2.4 テスト結果

- 6 デザイン ファイル

- 7 ソフトウェア ファイル

- 8 関連資料

- 9 用語

- 10著者について

- 11改訂履歴

5.1.1 ハードウェアの設定

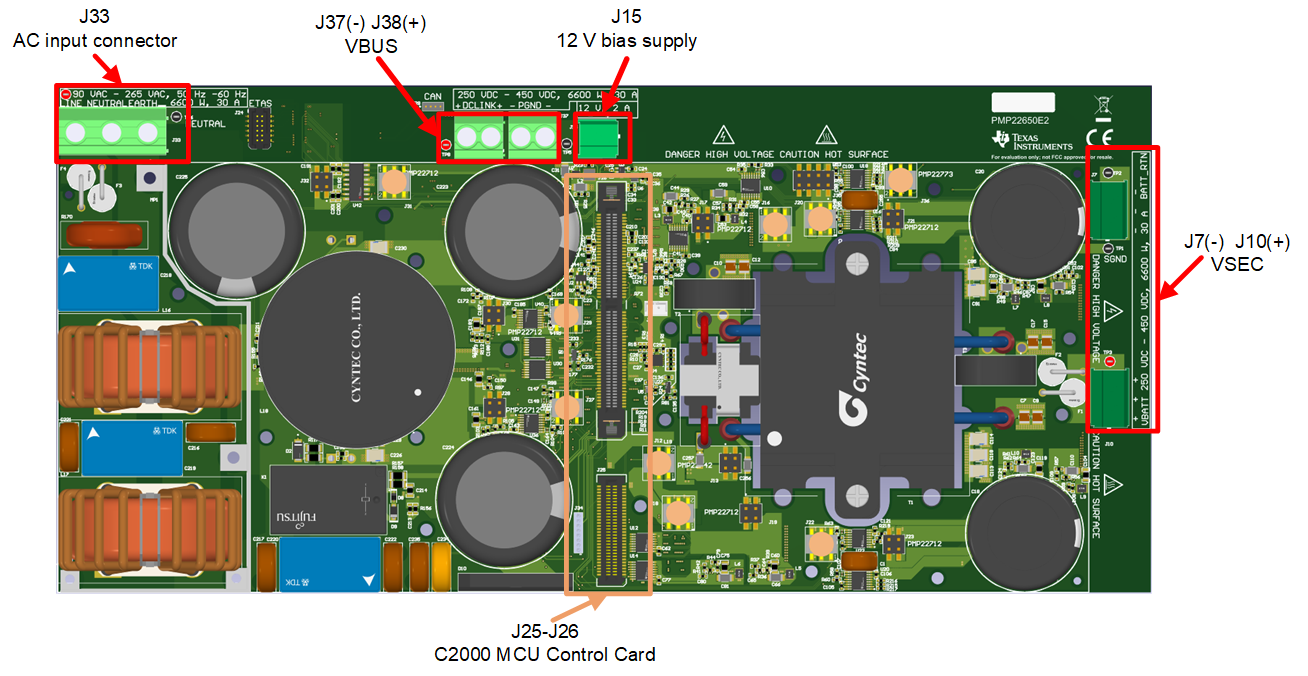

このデザインは高速エッジ カード (HSEC) の制御カード コンセプトを採用しており、HSEC 制御カードを利用できる C2000 マイクロコントローラ製品ファミリのデバイスであれば使用できる可能性があります。マイクロコントローラ の電力段の制御に使用される主要なリソースを 表 5-1 に示します。このリファレンス デザインの主要な電力段とコネクタを 図 5-1 に示します。表 5-3に主要なコネクタとその機能を示します。

- 基板に電源が接続されていないことを確認します。

- J25 スロットに制御カードを挿入します。

- 図 5-1 に示す J15 に、12V バイアス電源 (+12V、2A) の電源を接続します (電源は投入しないでください)。

- バイアス電源の電源をオンにします。制御カードの緑色の LED が点灯します。これは、C2000 マイクロコントローラ デバイスに電力が供給されていることを示します。注:マイクロコントローラの電源バイアスは電力段と分離されているため、この一連の指示でシステムを安全に立ち上げることができます。

- JTAG を接続するには、制御カードから USB ケーブルを使用してホスト コンピュータに接続します。

- TTPPLPFC 段を動作させるには、AC 入力を J33 (90V~264V) に接続する必要があります。テストには 10kW を超える電源が使用されていますが、低消費電力テストのみを実施する場合は、クリーンで安定した低定格電源を使用できます。

- PFC 段のスタンドアローン動作の場合、負荷を J37 と J38 に接続することができますし、代わりに CLLLC を使用して PFC 段に負荷をかけることもできます。

- CLLLC 段のスタンドアローン動作の場合、DC 電源 (400V) を J15 の VBUS に接続することができます。この場合、ソフトウェアで TTPLPFC を起動せず、上記ステップ 6 で説明した AC 電源は接続しないでください。

- 使用時は、CLLLC コンバータの 2 次側に負荷を接続する必要があります。このような負荷の接続には、J7 と J10 を使用できます。

- PFC 段と DCDC 段の両方を動作させる場合は、上記ステップ 6 のように AC 電源を接続し、上記ステップ 9 のように負荷を接続します。VBUS への接続は必要はありませんが、OBC 実行後に余分な電圧を迅速に逃がすために、電流ブリード抵抗が役立つ場合があります。

- 電流プローブと電圧プローブを接続して、1 次側と 2 次側のタンク電流を観測できます。オプションとして、電力計を接続して効率を測定することもできます。

図 5-1 基板の概要

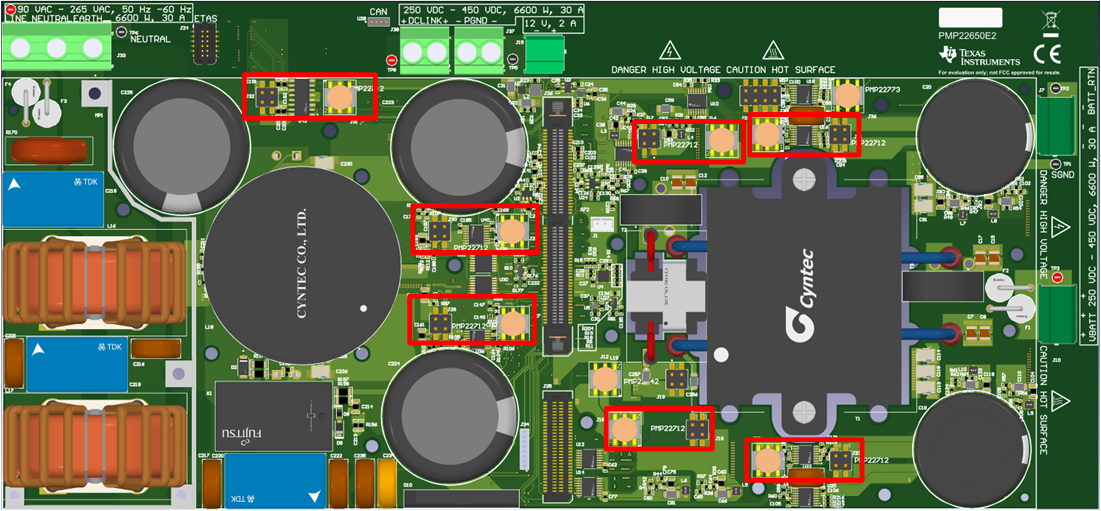

図 5-1 基板の概要赤色で示したバイアス電源ドーター カード 7 枚が必要です。

図 5-2 PMP22712 - バイアス電源

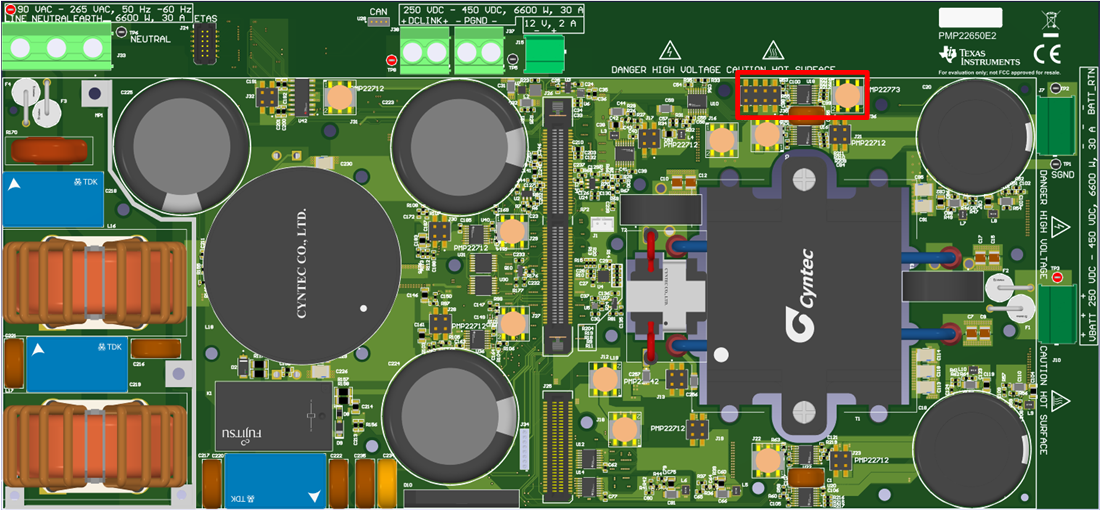

図 5-2 PMP22712 - バイアス電源赤色で示したフィードバック絶縁ドーター カード PMP22773 1 枚が必要です。

図 5-3 PMP22773 –フィードバック絶縁ドーター カード

図 5-3 PMP22773 –フィードバック絶縁ドーター カード| 信号名 | HSEC ピン番号 | F28003x ペリフェラル |

|---|---|---|

| SYSTEM ISR Trigger | - | ECAP1 |

| CLLLC_CONTROL_OUTPUT_DAC_PIN | 14 | DACA |

| CLLLC_PRIM_LEG1_H/L | 49/51 | EPWM1 (A/B) |

| CLLLC_PRIM_LEG2_H/L | 53/55 | EPWM2 (A/B) |

| CLLLC_SEC_LEG1_H/L | 50/52 | EPWM3 (A/B) |

| CLLLC_SEC_LEG2_H/L | 54/56 | EPWM4 (A/B) |

| CLLLC_FAULTn | 74 | GPIO-23 → INPUTXBAR2 |

| CLLLC_LC_CHANGE | 62 | GPIO-14 |

| CLLLC_SEC_SIDE_DIAG | 80 | GPIO-30 |

| TTPLPFC_LOW_FREQ_H/L | 57/59 | EPWM5 (A/B) |

| TTPLPFC_HIGH_FREQ_PH1_H/L | 61/63 | EPWM6 (A/B) |

| TTPLPFC_HIGH_FREQ_PH2_H/L | 58/60 | EPWM7 (A/B) |

| TTPLPFC_FAULTn | 72 | GPIO-22 → INPUTXBAR1 |

| TTPLPFC_INRUSH_RELAY_CTRL | 64 | GPIO-15 |

| ERRORSTSn | 102 | GPIO55 |

|

SYSTEM_WATCHDOG_OUT SYSTEM_WATCHDOG_DISABLE SYSTEM_PMIC_SPI (予約済み) SYSTEM_PMIC_SPI (予約済み) |

75 77 79 81 |

GPIO24 GPIO25 (抵抗オプション) GPIO26 (抵抗オプション) GPIO27 (抵抗オプション) |

| SYSTEM_DISABLE_FET_SUPPLY | 85 | GPIO32 |

|

SYSTEM_TEMP_MUX_OUT1 SYSTEM_TEMP_MUX_OUT2 |

91 96 |

GPIO41 -> ECAP2 → INPUTXBAR3 GPIO60 -> ECAP3 → INPUTXBAR4 |

| SYSTEM_TEMP_MUX_SEL_1-3 |

93 94 95 |

GPIO47 GPIO58 GPIO59 |

|

SYSTEM_PROFILING1~3 |

89 92 101 |

GPIO40 GPIO44 GPIO49 |

|

FSI_TX_D0 FSI_TX_D1 FSI_TX_CLK |

101 103 105 |

GPIO-49/FSITXA_D0 GPIO-50/FSITXA_D1 GPIO-51/FSITXA_CLK |

|

LED1 LED2 |

82 86 |

GPIO-31 → LED1 GPIO-34 → LED2 (SFRA) |

この表はリファレンス デザインのサンプリング方法を示し、上部の列はそれぞれ 1 つの独立した ADC を表しています。各 ADC は互いに完全に独立して動作します。各信号には、1 つまたは複数の変換開始 (SOC) が割り当てられます。各 SOC はそのチャネルの独立した 1 つの読み取りを表し、たとえば、TTPLPFC_IAC_PH1 は ADCA 内の SOC0 と SOC1 に割り当てられています。つまり、この信号はサイクルごとに 2 回サンプリングされ、1 回は ePWM6_SOCA によってトリガされ、もう 1 回は ePWM6_SOCB によってトリガされるのです。このトリガは 120kHz で動作しているため、この信号は各 120kHz のサンプリング期間中、実質的には 2 倍のオーバーサンプリングが行われます。同様に、CLLLC_ISEC では 11 倍のオーバーサンプリングが行われ、CLLLC_IPRIM はオーバーサンプリングされません。また、この表には、低周波サンプリング信号がいくつか示されており、これらの信号が異なる SOC 信号を使用していることがわかります。最後に、SOC を番号順に処理するためにラウンド ロビン カウンタが使用されているため、表はサンプリングの順に上から下へ時系列に読み取れます。

| ADC-A | ADC-B | ADC-C | |

|---|---|---|---|

|

最も優先度の高い信号 (120kHz) |

TTPLPFC_IAC_PH1 (A2、CMPSS1) SOC0 → ADC_TRIGGER_EPWM6_SOCA SOC1 → ADC_TRIGGER_EPWM6_SOCB |

TTPLPFC_IAC_PH2 (B12、CMPSS3) SOC0 → ADC_TRIGGER_EPWM6_SOCA SOC1 → ADC_TRIGGER_EPWM6_SOCB |

TTPLPFC_VAC (C7) SOC0 → ADC_TRIGGER_EPWM6_SOCA SOC1 → ADC_TRIGGER_EPWM6_SOCB |

|

CLLLC_ISEC (A5、CMPSS2) SOC2 → ADC_TRIGGER_EPWM6_SOCA SOC3 → ADC_TRIGGER_EPWM6_SOCA SOC4 → ADC_TRIGGER_EPWM6_SOCA SOC5 → ADC_TRIGGER_EPWM6_SOCA SOC6 → ADC_TRIGGER_EPWM6_SOCA SOC7 → ADC_TRIGGER_EPWM6_SOCA SOC8 → ADC_TRIGGER_EPWM6_SOCB SOC9 → ADC_TRIGGER_EPWM6_SOCB SOC10 → ADC_TRIGGER_EPWM6_SOCB SOC11 → ADC_TRIGGER_EPWM6_SOCB SOC12 → ADC_TRIGGER_EPWM6_SOCB |

TTPLPFC_VBUS / CLLLC_VBUS (B4) SOC2 → ADC_TRIGGER_EPWM6_SOCA SOC3 → ADC_TRIGGER_EPWM6_SOCB SOC4 → ADC_TRIGGER_EPWM7_SOCA SOC5 → ADC_TRIGGER_EPWM7_SOCB |

CLLLC_VSEC (C11、CMPSS2) SOC2 → ADC_TRIGGER_EPWM6_SOCA SOC3 → ADC_TRIGGER_EPWM6_SOCA SOC4 → ADC_TRIGGER_EPWM6_SOCA SOC5 → ADC_TRIGGER_EPWM6_SOCA SOC6 → ADC_TRIGGER_EPWM6_SOCA SOC7 → ADC_TRIGGER_EPWM6_SOCA SOC8 → ADC_TRIGGER_EPWM6_SOCA SOC9 → ADC_TRIGGER_EPWM6_SOCA SOC10 → ADC_TRIGGER_EPWM6_SOCA SOC11 → ADC_TRIGGER_EPWM6_SOCA SOC12 → ADC_TRIGGER_EPWM6_SOCA |

|

|

CLLLC_IPRIM (A9、CMPSS2) SOC13 → ADC_TRIGGER_EPWM1_SOCA |

|||

|

低周波サンプリング信号 (10kHz) |

TTPLPFC_VAC_L (A4) SOC14 → ADC_TRIGGER_CPU1_TINT2 |

TTPLPFC_VAC_N (B2) SOC10 → ADC_TRIGGER_CPU1_TINT2 |

TTPLPFC_VBUS2 (C10、CMPSS2) SOC14 → ADC_TRIGGER_CPU1_TINT2 |

|

SYSTEM_ TEMP_1 (A11) SOC15 → ADC_TRIGGER_CPU1_TINT2 |

SYSTEM_VREF_1_65 (B5) SOC11 → ADC_TRIGGER_CPU1_TINT2 |

CLLLC_VSEC (C11、CMPSS2) VSEC13 → SOC15 → ADC_TRIGGER_CPU1_TINT2 |

|

| サンプリングなし、CMPSS のみ | CLLLC_IPRIM_TANK (A12/C5、CMPSS2) | CLLLC_ISEC_TANK (C1、CMPSS4) |

| コネクタ名 | 機能 |

|---|---|

| J33 | AC 入力 |

| J37/J38 | VBUS 接続、PFC 出力、DCDC VPRIM |

| J7/J10 | DCDC 出力接続、 DCDC VSEC |

| J15 | 12V、2A 電源 |

| J25/J26 | HSEC 制御カードのコネクタ スロット |