JAJU922A October 2022 – February 2024

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1 CLLLC システムの説明

- 2 CLLLC システムの概要

- 3 トーテムポール PFC システムの説明

- 4 主な使用製品

-

5 ハードウェア、ソフトウェア、試験要件、試験結果

- 5.1 必要なハードウェアとソフトウェア

- 5.2

テストと結果

- 5.2.1 テストのセットアップ (初期設定)

- 5.2.2

CLLLC のテスト手順

- 5.2.2.1 ラボ 1.1 次側から 2 次側への電力フロー、PWM ドライバの開ループ チェック

- 5.2.2.2 ラボ 2.1 次側から 2 次側への電力フロー、PWM ドライバおよび保護付き ADC の開ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.3 ラボ 3.1 次側から 2 次側への電力フロー、閉電圧ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.4 ラボ 4.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.5 ラボ 5.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側で抵抗性負荷が電圧源と並列に接続されてバッテリ接続をエミュレートしている状態)

- 5.2.3 TTPLPFC のテスト手順

- 5.2.4 テスト結果

- 6 デザイン ファイル

- 7 ソフトウェア ファイル

- 8 関連資料

- 9 用語

- 10著者について

- 11改訂履歴

5.2.2.5.2 電流ループ補償器の設計

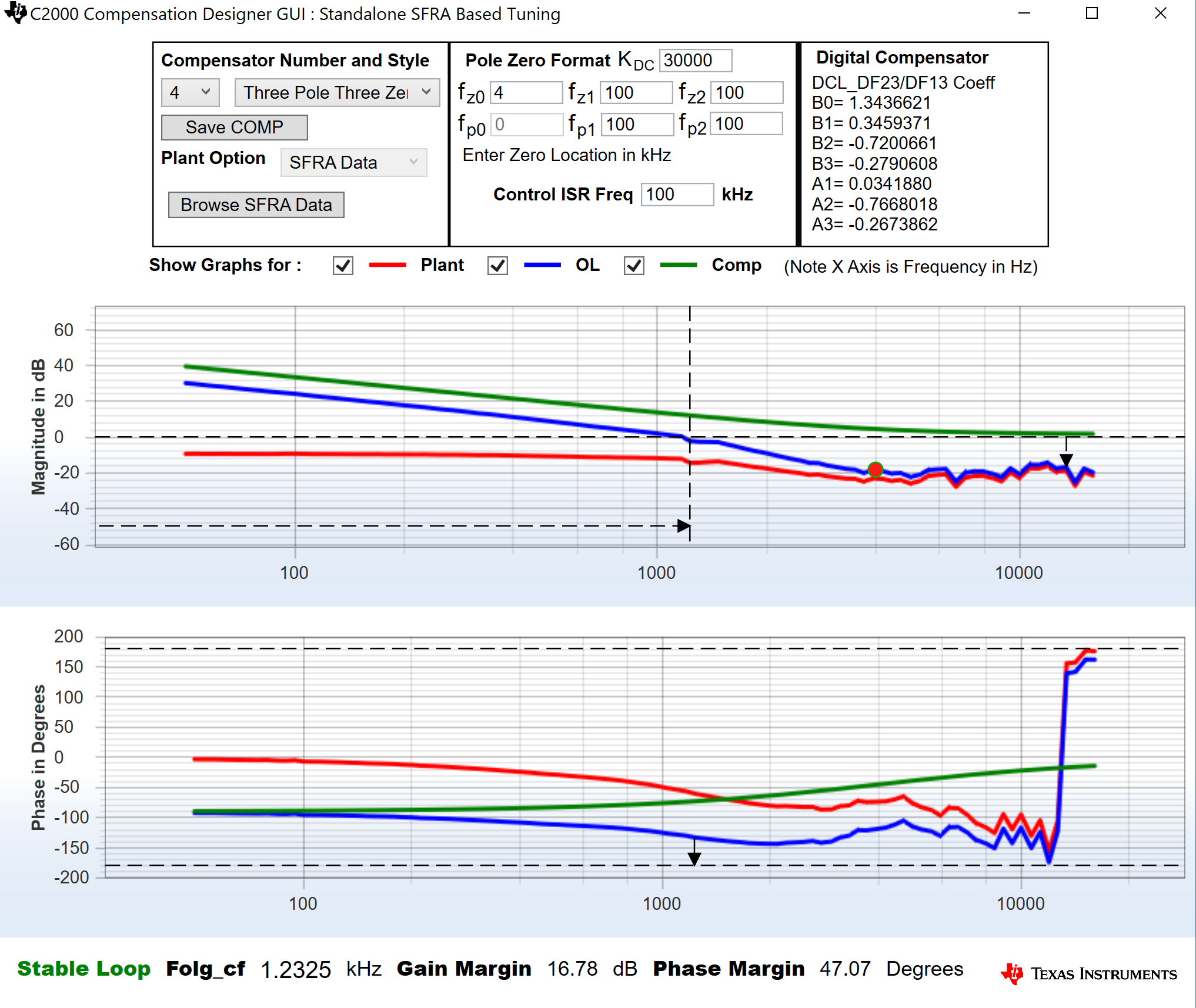

- Compensation Designer が起動します。現在のところ、数学モデルが利用できないため、この基板で行われた調整を利用して、以下のような補償が設計されています。バッテリ エミュレーション モードのプラントではゲインが大きくなるため、それに対応するために係数を下げる必要があります。図 5-28 に、このラボでこのデザインに使用されている各係数を示します。

図 5-28 ラボ 5、Compensation Designer

図 5-28 ラボ 5、Compensation Designer - 補償器の設計が完了したら、CLLLC_settings.h ファイルで補償器の値を更新できます。係数は控えめにして、ラボ 3 で使用したものよりもはるかに低くするのが最善です。

- Compensation Designer を閉じます。

- このビルドでは、settings.h ファイルに以下の定義が設定されています。

#if CLLLC_LAB == 5 #define CLLLC_CONTROL_RUNNING_ON 1 #define CLLLC_POWER_FLOW CLLLC_POWER_FLOW_PRIM_SEC #define CLLLC_INCR_BUILD CLLLC_CLOSED_LOOP_BUILD #define CLLLC_CONTROL_MODE CLLLC_CURRENT_MODE #define CLLLC_TEST_SETUP CLLLC_TEST_SETUP_EMULATED_BATTERY #define CLLLC_PROTECTION CLLLC_PROTECTION_ENABLED #if CLLLC_SFRA_ALLOWED == 1 #define CLLLC_SFRA_TYPE CLLLC_SFRA_CURRENT #else #define CLLLC_SFRA_TYPE CLLLC_SFRA_DISABLED #endif #define CLLLC_SFRA_AMPLITUDE (float32_t)CLLLC_SFRA_INJECTION_AMPLITUDE_LEVEL1 #endif