JAJU922A October 2022 – February 2024

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1 CLLLC システムの説明

- 2 CLLLC システムの概要

- 3 トーテムポール PFC システムの説明

- 4 主な使用製品

-

5 ハードウェア、ソフトウェア、試験要件、試験結果

- 5.1 必要なハードウェアとソフトウェア

- 5.2

テストと結果

- 5.2.1 テストのセットアップ (初期設定)

- 5.2.2

CLLLC のテスト手順

- 5.2.2.1 ラボ 1.1 次側から 2 次側への電力フロー、PWM ドライバの開ループ チェック

- 5.2.2.2 ラボ 2.1 次側から 2 次側への電力フロー、PWM ドライバおよび保護付き ADC の開ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.3 ラボ 3.1 次側から 2 次側への電力フロー、閉電圧ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.4 ラボ 4.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側に抵抗性負荷が接続されている状態)

- 5.2.2.5 ラボ 5.1 次側から 2 次側への電力フロー、閉電流ループ チェック (2 次側で抵抗性負荷が電圧源と並列に接続されてバッテリ接続をエミュレートしている状態)

- 5.2.3 TTPLPFC のテスト手順

- 5.2.4 テスト結果

- 6 デザイン ファイル

- 7 ソフトウェア ファイル

- 8 関連資料

- 9 用語

- 10著者について

- 11改訂履歴

5.2.4.5 熱データ

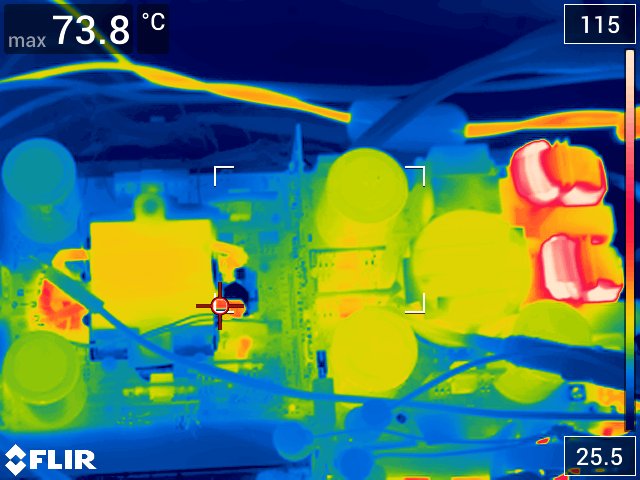

図 5-51 は全負荷動作時に撮影されたものです。発熱が著しい部品はすべて、基板底面のコールド プレートに接続されています。この画像で最も高温に見えている部品は、EMI フィルタ内にある同相モード インダクタに起因するものです。これらの部品はコールド プレートに接続されておらず、冷却はすべて周囲の空気を通してのみ行われます。

図 5-51 上面の熱画像

図 5-51 上面の熱画像GaN FET の温度は、LMG3522 デバイスに搭載されているオンボード温度センサで測定されます。全負荷条件では、すべての FET 温度は 75℃ を下回ります。

表 5-5 に、以下の条件における GaN FET の測定温度を示します。

- VIN,AC:240V

- VDC,LINK:400V

- クーラント温度:33°C

表 5-5 GaN FET 測定温度

| GaN FET | 温度 (℃) |

|---|---|

| PFC | 66.8 |

| CLLLC 1 次側 (350V/19A) | 58.1 |

| CLLLC 2 次側 (350V/19A) | 59.5 |

| CLLLC 1 次側 (300V/19A) | 61.0 |

| CLLLC 2 次側 (300V/19A) | 74.0 |

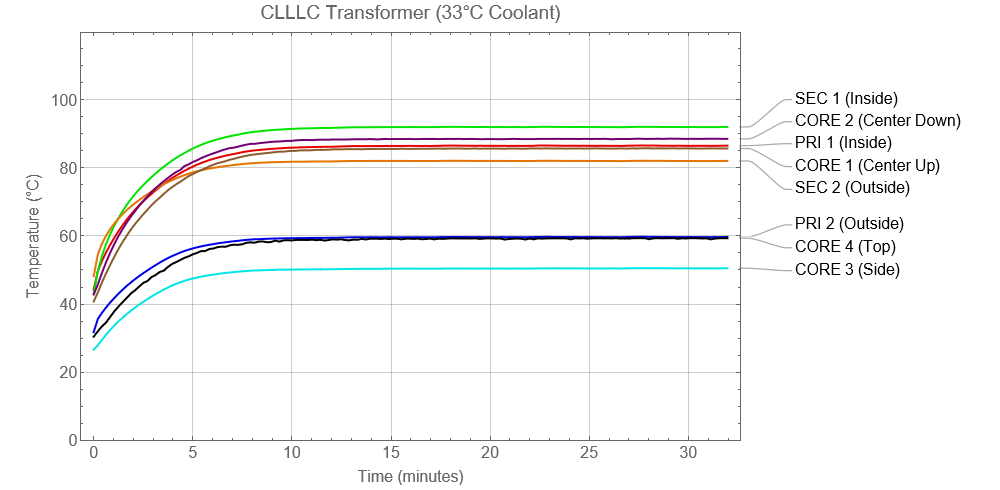

図 5-52 に、以下の条件におけるトランスの臨界温度を示します。

- クーラント温度:33°C

- トランスの温度測定位置

- PRI 1 – 1 次側巻線の内側表面で測定

- PRI 2 – 1 次側巻線の外側表面で測定

- SEC 1 – 2 次側巻線の内側表面で測定

- SEC 2 – 2 次側巻線の外側表面で測定

- CORE 1 – コアのセンターレッグ上部で測定

- CORE 2 – コアのセンターレッグ下部で測定

- CORE 3 – コアの側面で測定

- CORE 4 – コアの上部で測定

図 5-52 CLLLC トランスの温度

図 5-52 CLLLC トランスの温度