JAJU926 March 2024

4.1 ハードウェア要件

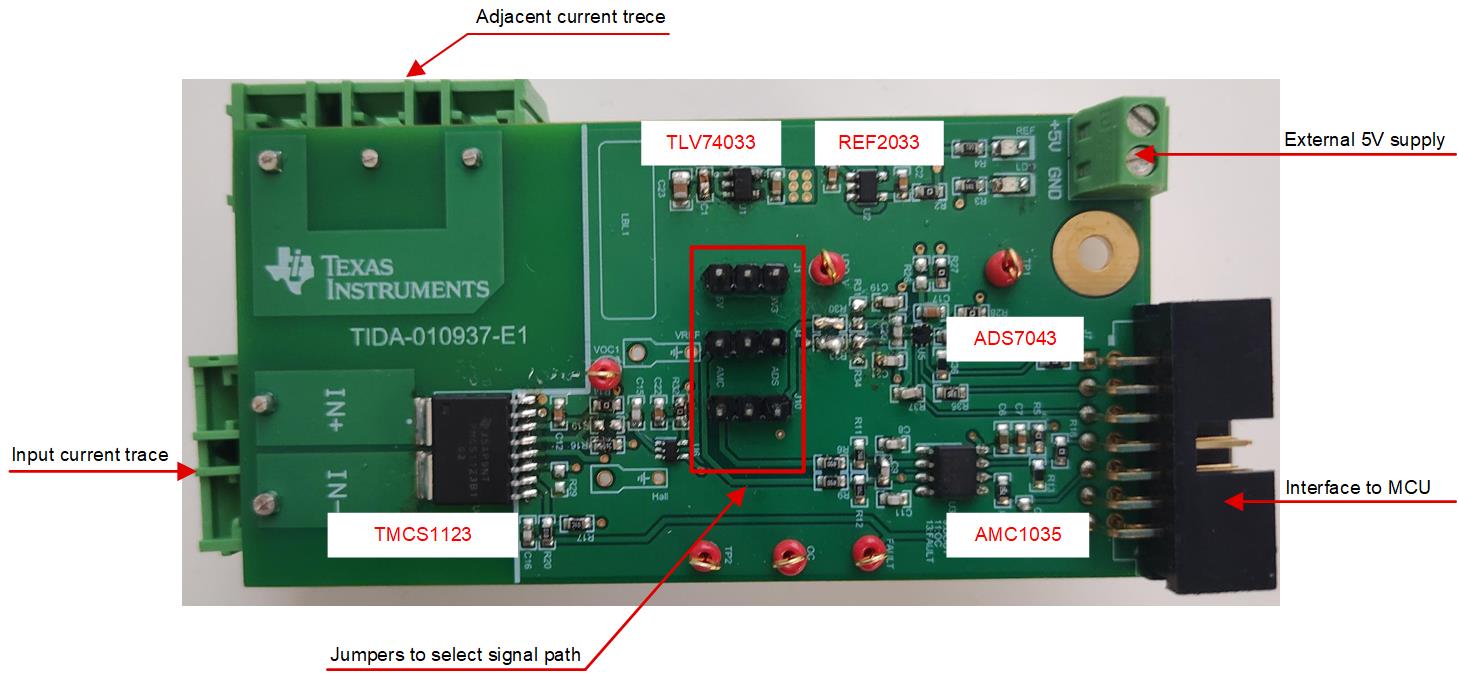

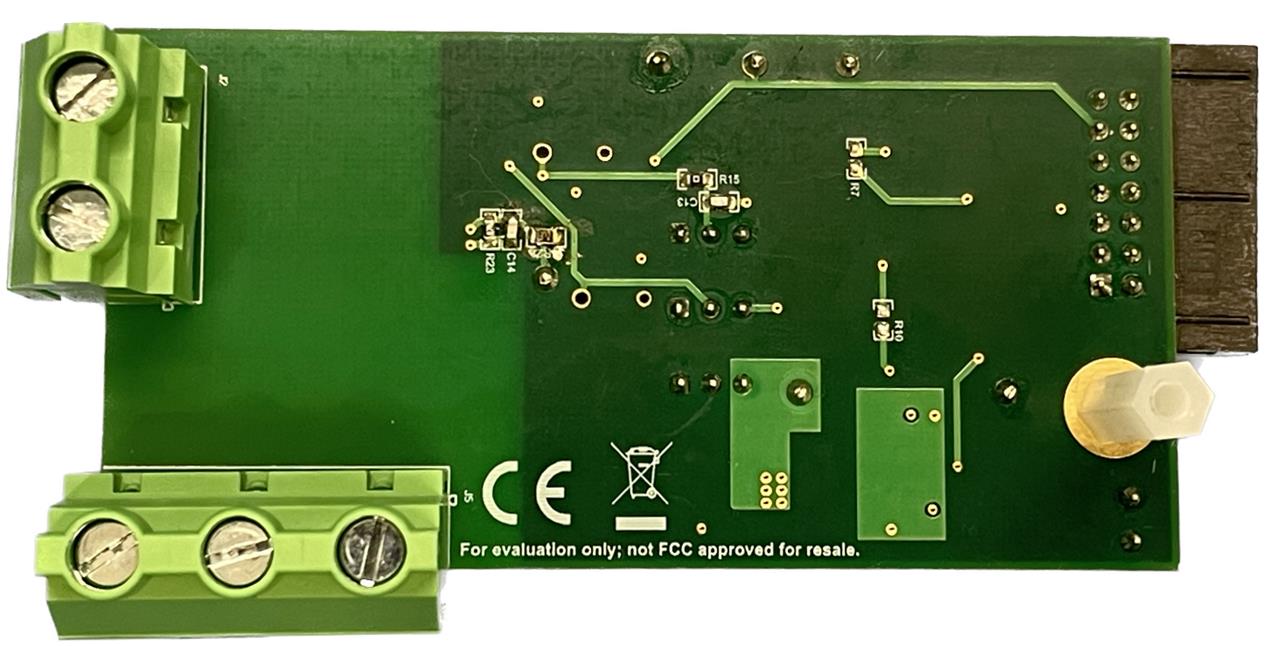

図 4-1 および 図 4-2 に、プリント基板 (PCB) の上面図と底面図、および 主なデバイス、入力電流、MCU とのインターフェイスとなる I/O コネクタ、デザインを構成するためのジャンパの概略を示します。

図 4-1 TIDA-010937 PCB の上面図

図 4-1 TIDA-010937 PCB の上面図 図 4-2 TIDA-010937 PCB の 底面図

図 4-2 TIDA-010937 PCB の 底面図ヘッダおよびデフォルトのジャンパ設定については、表 4-1 および 表 4-2 で説明します。

表 4-1 デフォルトの抵抗およびジャンパ設定

| ヘッダ、抵抗 | ジャンパ、抵抗の設定 |

|---|---|

| J1 | 3.3V 電源に接続 |

| J4 | ADS7043 に接続 |

| J10 | ADS7043 に接続 |

| R26、R27 | R27 を実装して、REF2033 からの 3.3V 電源供給を選択 |

表 4-2 ホスト MCU インターフェイス J7

| ヘッダ | 信号 | I/O |

|---|---|---|

| J7-1 | ADS7043 への SCLK | 3.3V 入力 |

| J7-3 | ADS7043 からの SDO | 3.3V 出力 |

| J7-5 | ADS7043 への CS | 3.3V 入力 |

| J7-7 | AMC1035 への CLK | 3.3V 入力 |

| J7-9 | AMC1035 からの DOUT | 3.3V 出力 |

| J7-11 | TMCS1123 からの OC | 3.3V 出力 |

| J7-13 | TMCS1123 からの FAULT | 3.3V 出力 |