JAJU926 March 2024

4.4.4 過電流応答

大電流パルスを生成するために、GaN ベースのハーフ ブリッジ回路 LMG3422EVM を使用します。図 4-16 に、テスト構成の概要を示し ます。

LMG3422EVM は、ドライバと保護機能を内蔵した LMG3422 600V GaN 電界効果トランジスタ (FET) を 2 個使ったハーフブリッジ構成を採用しており、必要なバイアス回路と、ロジックまたは電力のレベル シフト機能を備えています。GaN ハーフブリッジは、高スルーレートの出力電圧パルスを生成します。また、電流制限抵抗を使用して出力電流のピーク値を設定します。

図 4-16 過電流応答テスト構成

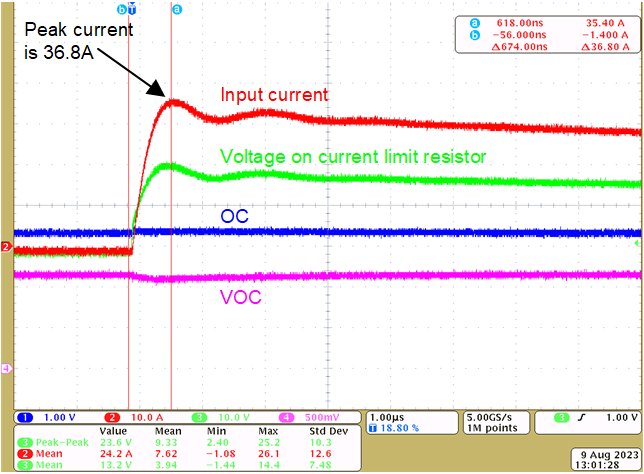

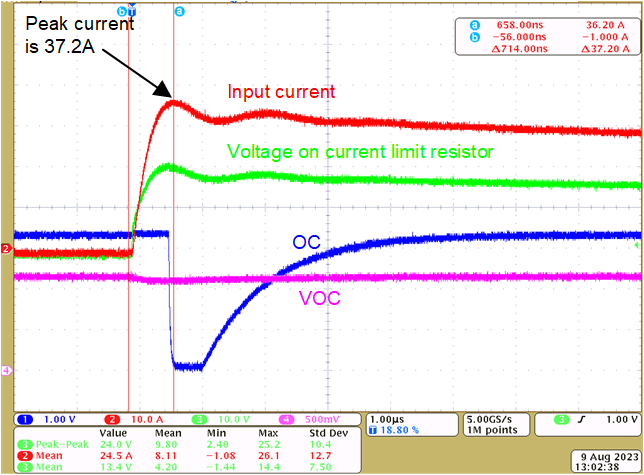

図 4-16 過電流応答テスト構成OC スレッショルドを検証するために、DC バス電圧を調整して、必要なピーク電流を TMCS1123 に注入します。図 4-17 および 図 4-18 に結果を示します。信号 VOUT は、TMCS1123 ホール センサのアナログ出力電圧です。VOC はアナログ入力であり、過電流スレッショルドを 37A に設定します。OC はアクティブ LOW のデジタル出力で、過電流が検出されると LOW になります。ピーク電流が 36.8A のとき OC はトリガされず、電流が 37.2A に増加すると OC がトリガされるので、スレッショルドは約 37A です。

図 4-17 OC スレッショルドの確認 (ピーク電流 = 36.8A)

図 4-17 OC スレッショルドの確認 (ピーク電流 = 36.8A) 図 4-18 OC スレッショルドの確認 (ピーク電流 = 37.2A)

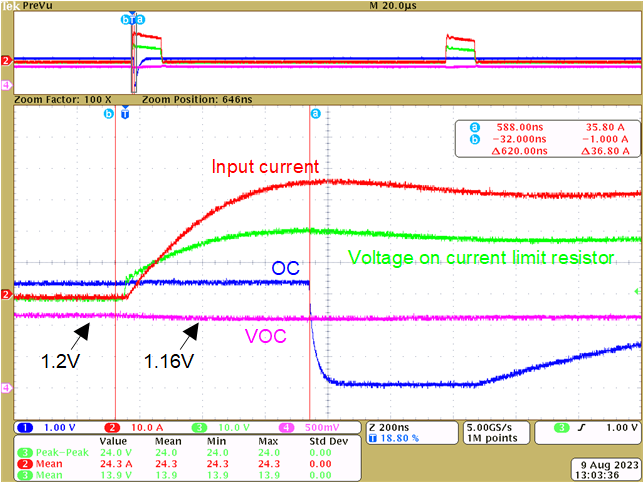

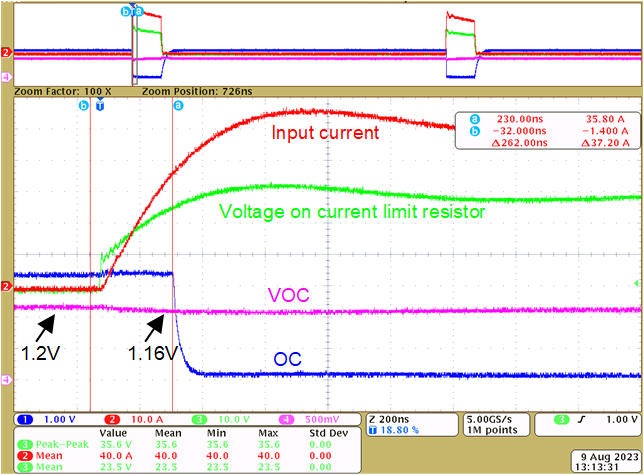

図 4-18 OC スレッショルドの確認 (ピーク電流 = 37.2A)次に、ピーク電流を連続的に増加させて OC 波形を観測します。図 4-19 で、ピーク電流は 37.2A であり、電流が 36.8A に達したとき OC がトリガされます。図 4-20 で、ピーク電流は 57.6A であり、電流が 37.2A に達したとき OC がトリガされます。電流の立ち上がり時に、VOC が 1.2V から 1.16V にわずかに低下します。これは、理論上のスレッショルドが 40A から 38.7A に低下することを意味します。実際のスレッショルドは 37A であり、データシートのスレッショルドの許容範囲内です。このテストは、TMCS1123 の過電流応答時間が非常に短く、電流がスレッショルドに達するとすぐに OC がトリガされることを示しています。

図 4-19 OC 応答テスト (ピーク電流 = 37.2A)

図 4-19 OC 応答テスト (ピーク電流 = 37.2A) 図 4-20 OC 応答テスト (ピーク電流 = 57.6A)

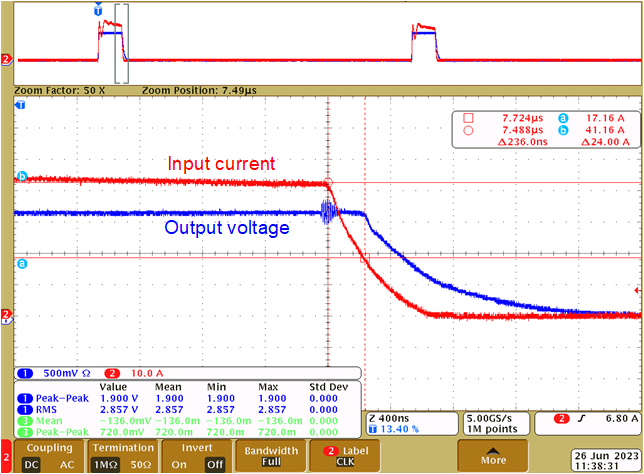

図 4-20 OC 応答テスト (ピーク電流 = 57.6A)OC イベント後の TMCS1123 出力電圧の動作を観測します。結果を 図 4-21 に示します。VOUT は、OC イベントの後 68ns で低下を開始します。

図 4-21 OC イベント後の VOUT 復帰時間

図 4-21 OC イベント後の VOUT 復帰時間