JAJU934 May 2024

4.3.3 SPI 信号測定

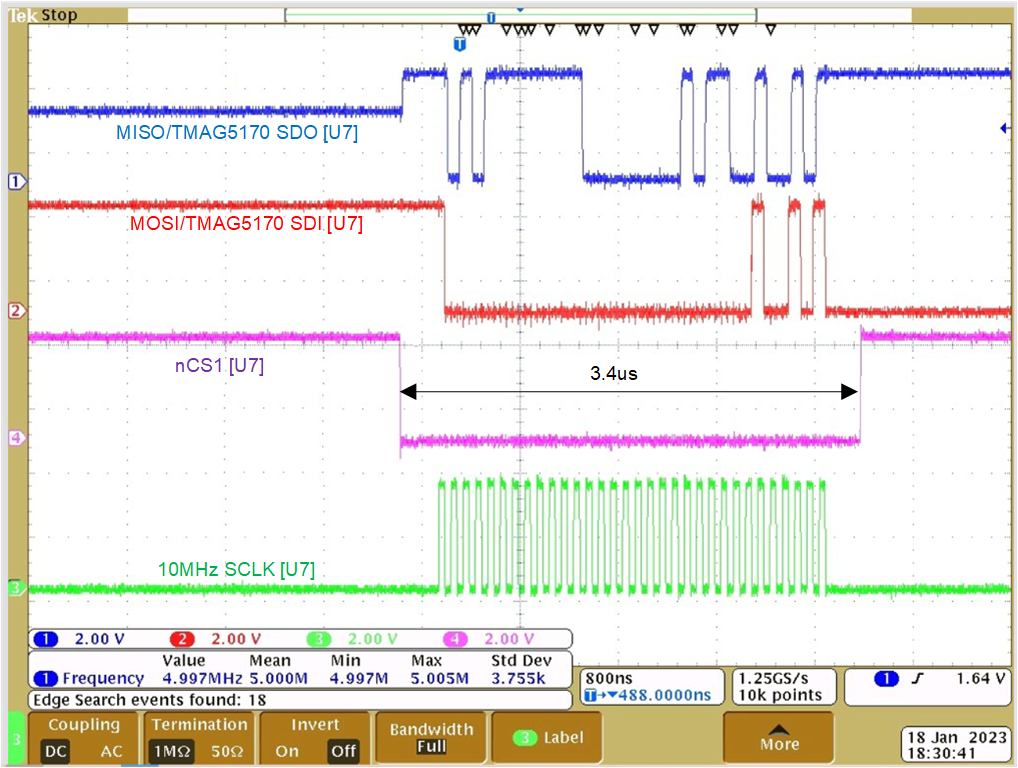

図 4-14 に、デイジーチェーン内の最初の TMAG5170 (U7) で測定された nCS1 のある 32 ビットの SPI タイミング フレームを示します。赤い信号は SDI 書き込みフレーム (読み取りコマンド) と、対応する特別な 32 ビット SDO 読み取りフレームであり、2 つの 12 ビット X および Z 磁界データ、ステータス ビット、CRC が含まれています。転送には 3.4μs かかります。

図 4-15 SPI 32 ビット フレーム タイミング

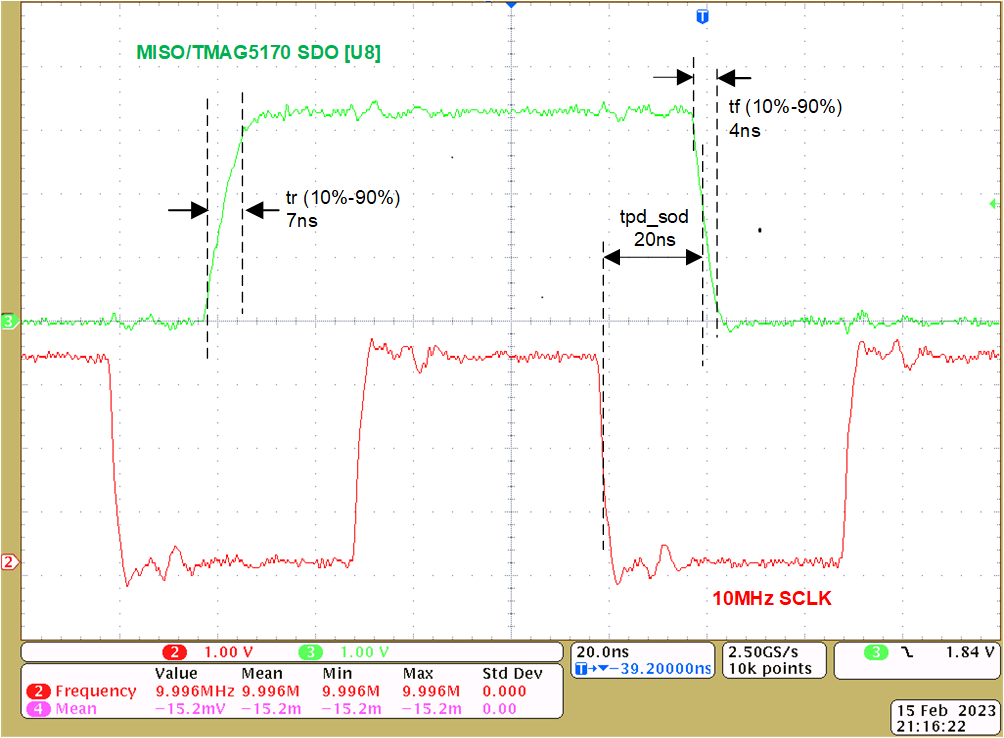

図 4-15 SPI 32 ビット フレーム タイミング図 4-15に、TMAG5170 (U7) SDO 出力と SPI クロック SCLK 入力のタイミングを示します。SDO 信号の立ち下がりクロック エッジに対する遅延時間は 20ns です。SDO の立ち上がり時間は 7ns、立ち下がり時間は 3ns です。

図 4-16 TMAG5170 U8 SDO (MISO) と SCLK

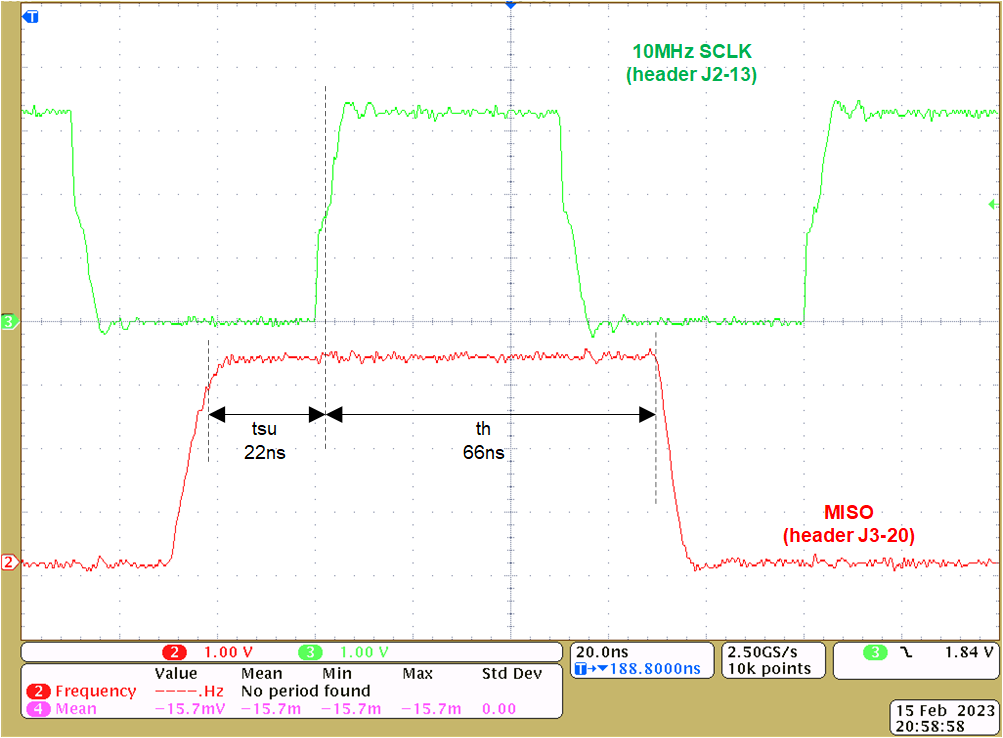

図 4-16 TMAG5170 U8 SDO (MISO) と SCLK図 4-16 に、TIDA-060045 MCU のヘッダ J3-20 および J2-13 における SDO 出力と SPI クロック SCLK 入力のタイミングを示します。セットアップ時間 tsu は 22ns、ホールド時間 th は立ち上がりクロック エッジに対して 66ns です。

図 4-17 MCU ヘッダ J2 および J3 の MISO および SCLK

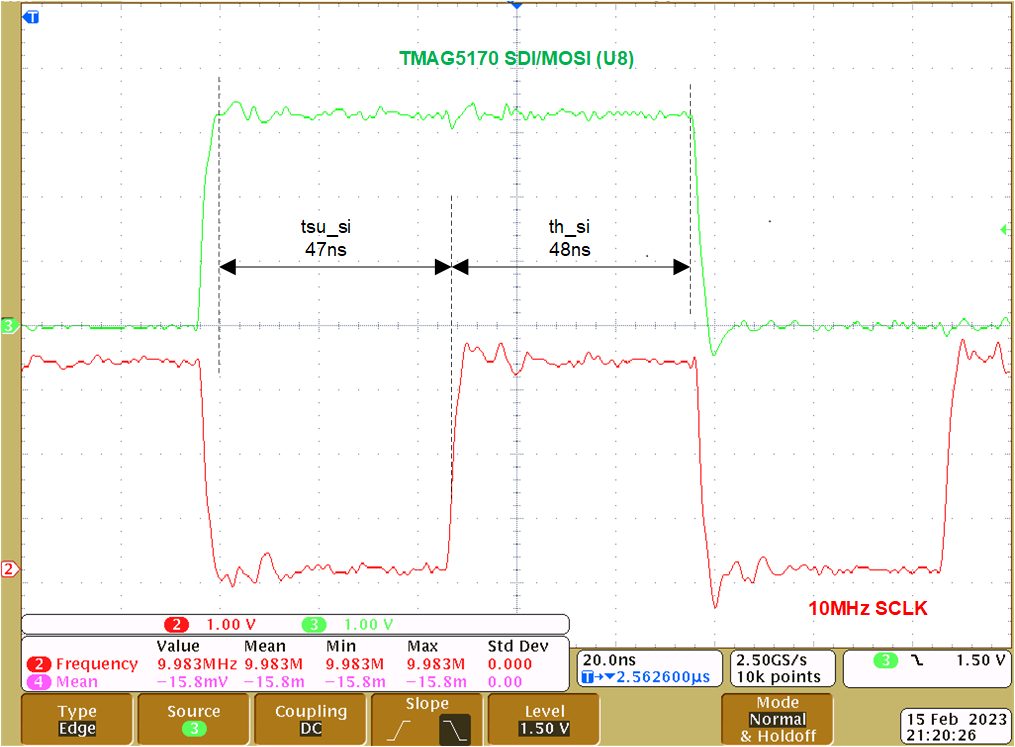

図 4-17 MCU ヘッダ J2 および J3 の MISO および SCLK図 4-17 に、TMAG5170 SDI 入力 (MOSI) と 10MHz SPI クロック (SCLK) のタイミングを示します。セットアップ時間 (tsu_si=47ns) とホールド時間 (th_si=48ns) の両方が、TMAG5170 の要件 (25ns (MIN)) を満たしています。

図 4-18 TMAG5170 U8 SDI (MOSI) および SCLK

図 4-18 TMAG5170 U8 SDI (MOSI) および SCLK以下の図は、SCLK デイジー チェーン内の最初の TMAG5170 MCU (U7) と最後の TMAG5170 (U8) で測定された SPI クロック (SCLK) 信号 (AC 並列終端ありとなし) の比較を示しています。

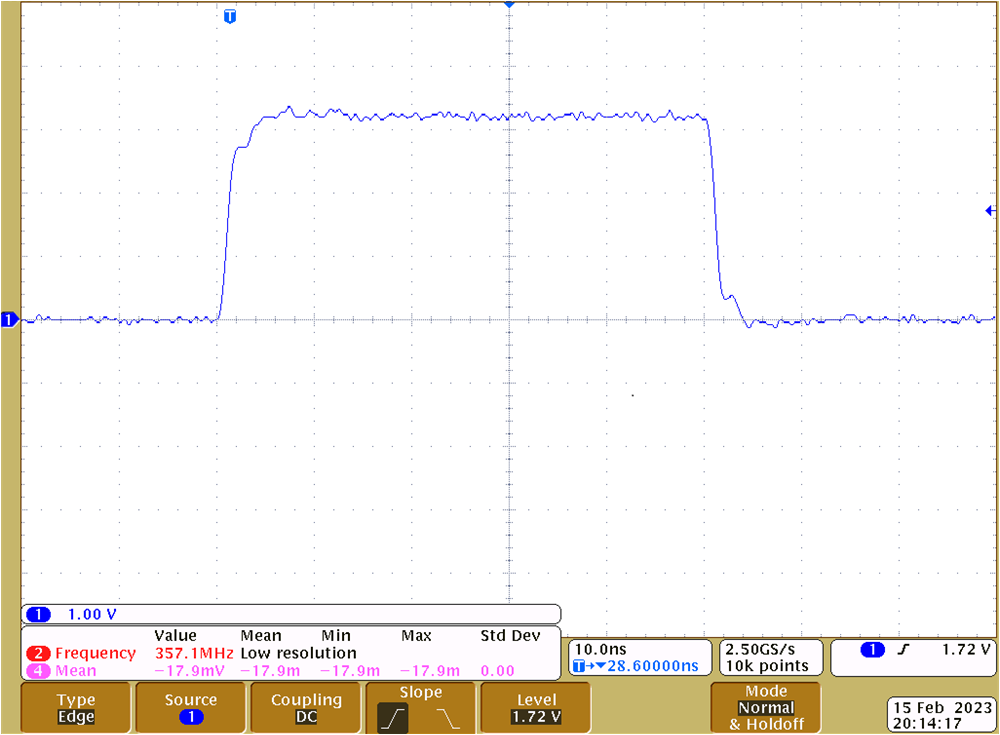

図 4-19 U7 での SCLK、U8 での AC 並列終端あり

図 4-19 U7 での SCLK、U8 での AC 並列終端あり 図 4-20 U7 での SCLK、U8 での AC 並列終端なし

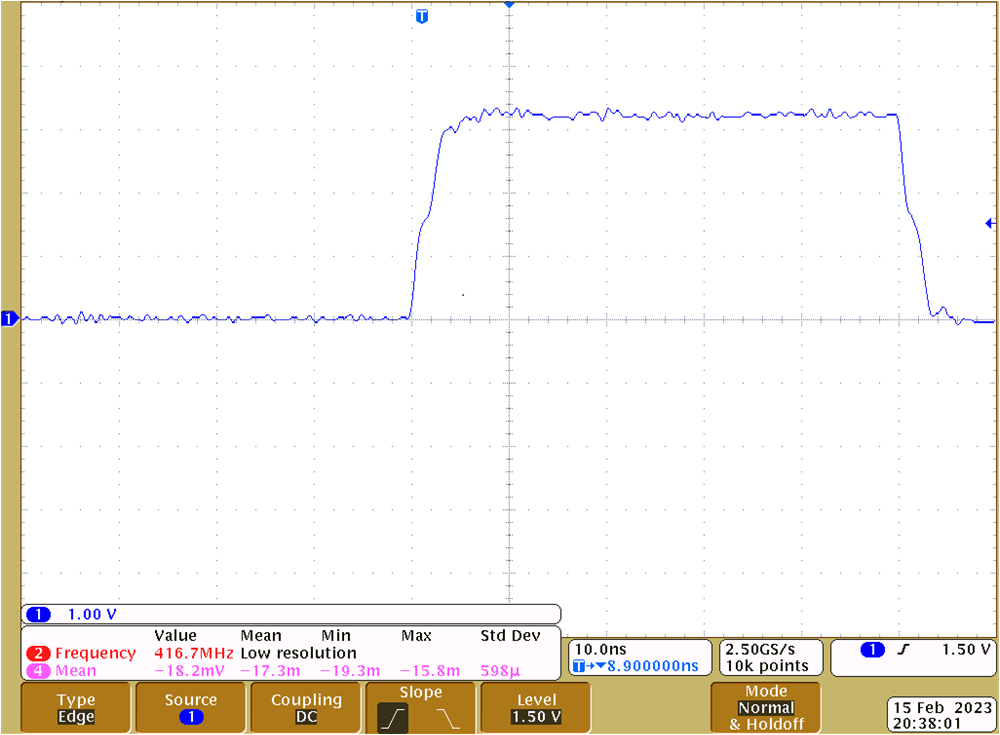

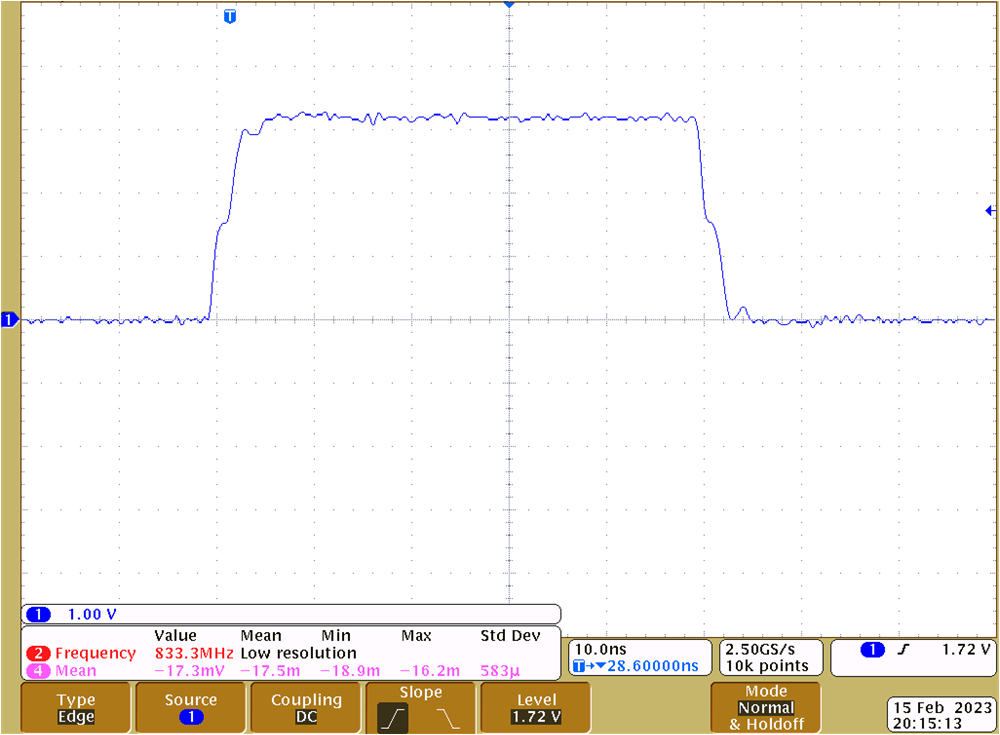

図 4-20 U7 での SCLK、U8 での AC 並列終端なし 図 4-21 U8 での SCLK、U8 での AC 並列終端あり

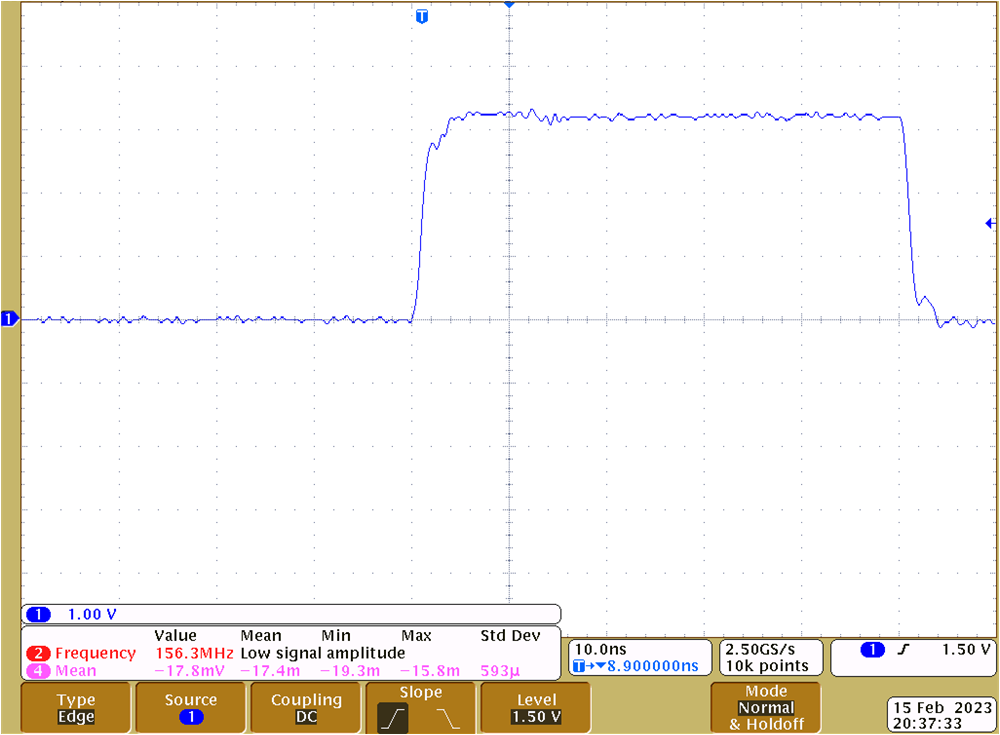

図 4-21 U8 での SCLK、U8 での AC 並列終端あり 図 4-22 U8 での SCLK、U8 での AC 並列終端なし

図 4-22 U8 での SCLK、U8 での AC 並列終端なしMCU 出力信号 nALERT、MOSI、SCLK、および nCS1~nCS4 に対する直列ライン終端抵抗は、MCH ヘッダの近くに 0Ω の直列ライン終端抵抗を備えています。これらの抵抗がデフォルトで 0Ω である理由は、TMS320F280049C LaunchPad 上の対応するパターンが TIDA-060045 と同等の長さであるためです。

TIDA-060045 の SPI パターンは 20cm (8 インチ) 未満です。対応する伝搬遅延は約 1.3ns で、立ち上がり時間や立ち下がり時間に比べてかなり短くなります。F280049C LaunchPad を接続した場合、AC 並列終端による大きな影響はありませんでした。

カスタム設計の場合、直列ライン終端抵抗は MCU の出力に直接配置する必要がありますが、TMS320F280049C LaunchPad を使用する場合はこれは不可能でした。SPI パターンの長さに応じて、AC 並列終端を考慮するかどうかが決まります。