JAJU934 May 2024

5.1.3.2 レイアウトのガイドライン

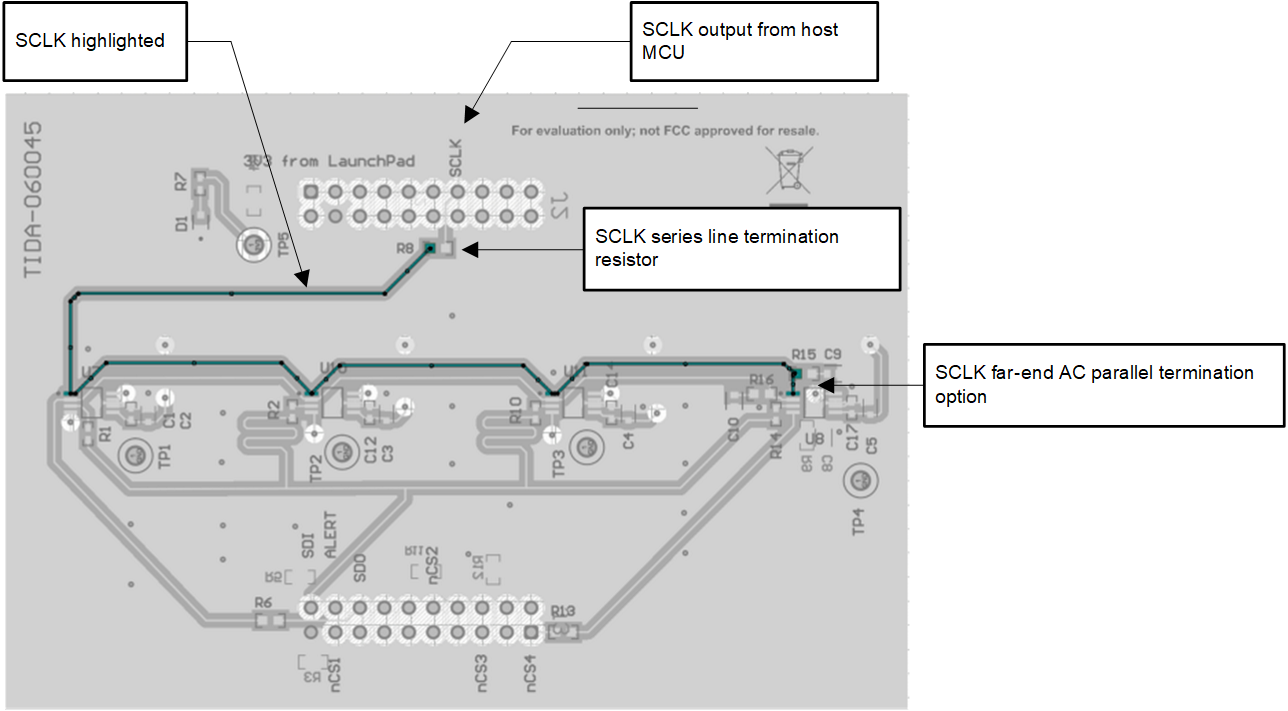

SPI クロック信号 SCLK のレイアウトを 図 5-1 に示します。SCLK は、デイジー チェーン接続の最上層で、最初の TMAG5170 (U7) から最後の TMAG5170 (U8) まで、シリアル ライン終端抵抗とオプションの遠端 AC 並列終端付きで配線されます。nALERT 信号と MOSI (TMAG5170 SDI) 信号は、同じ方法で配線されます。真ん中の 1 層下にある連続した GND プレーンが、帰路の GND として機能します。

図 5-1 SPI クロック (SCLK) パターンの配線

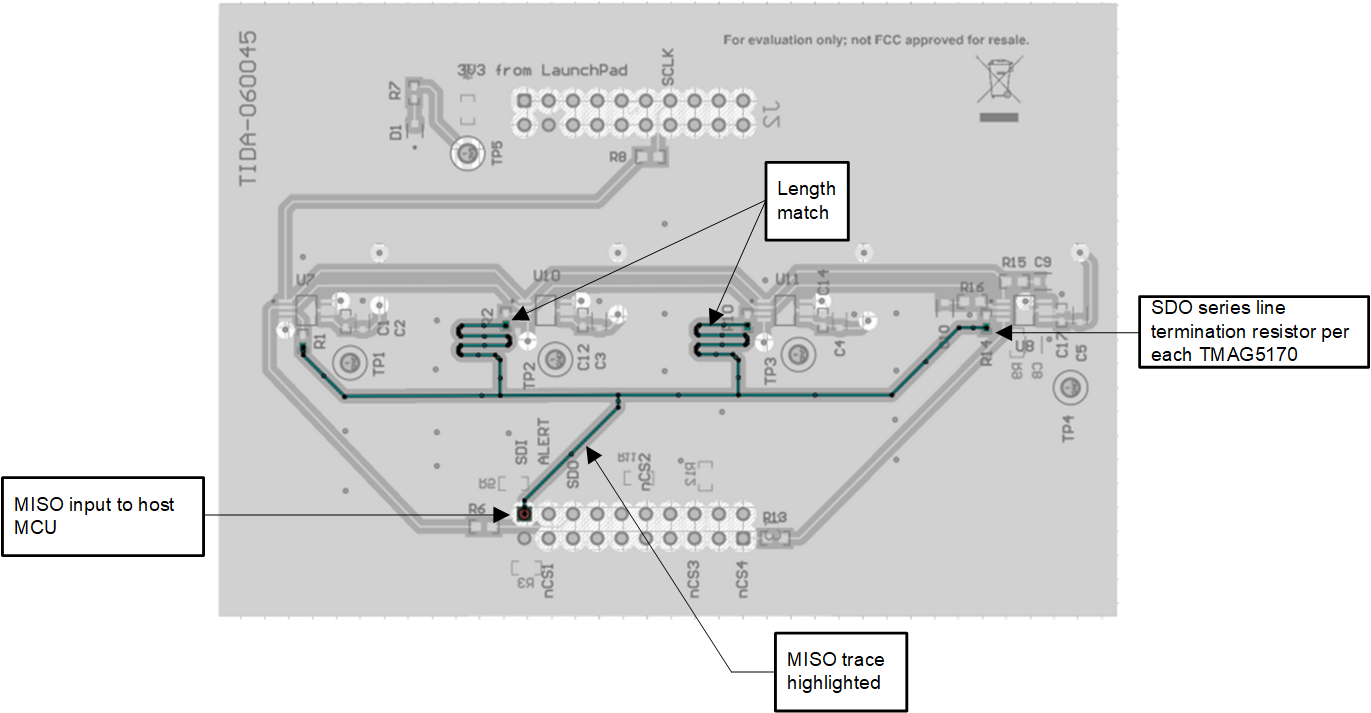

図 5-1 SPI クロック (SCLK) パターンの配線各 TMAG5170 の個別の SDO 出力 (SPI MISO) には、シリアル ライン終端抵抗があります。各 TMAG5170 からの 4 つの SDO パターンは、同様の長さでスター配線されてから、1 つのパターンにマージされてホスト プロセッサの MISO 入力ピンに接続されます。

図 5-2 MISO の長さが一致したスタートポロジ

図 5-2 MISO の長さが一致したスタートポロジ