JAJU936 May 2024

3.3.5 ディセーブル (シャットダウン) のテスト結果

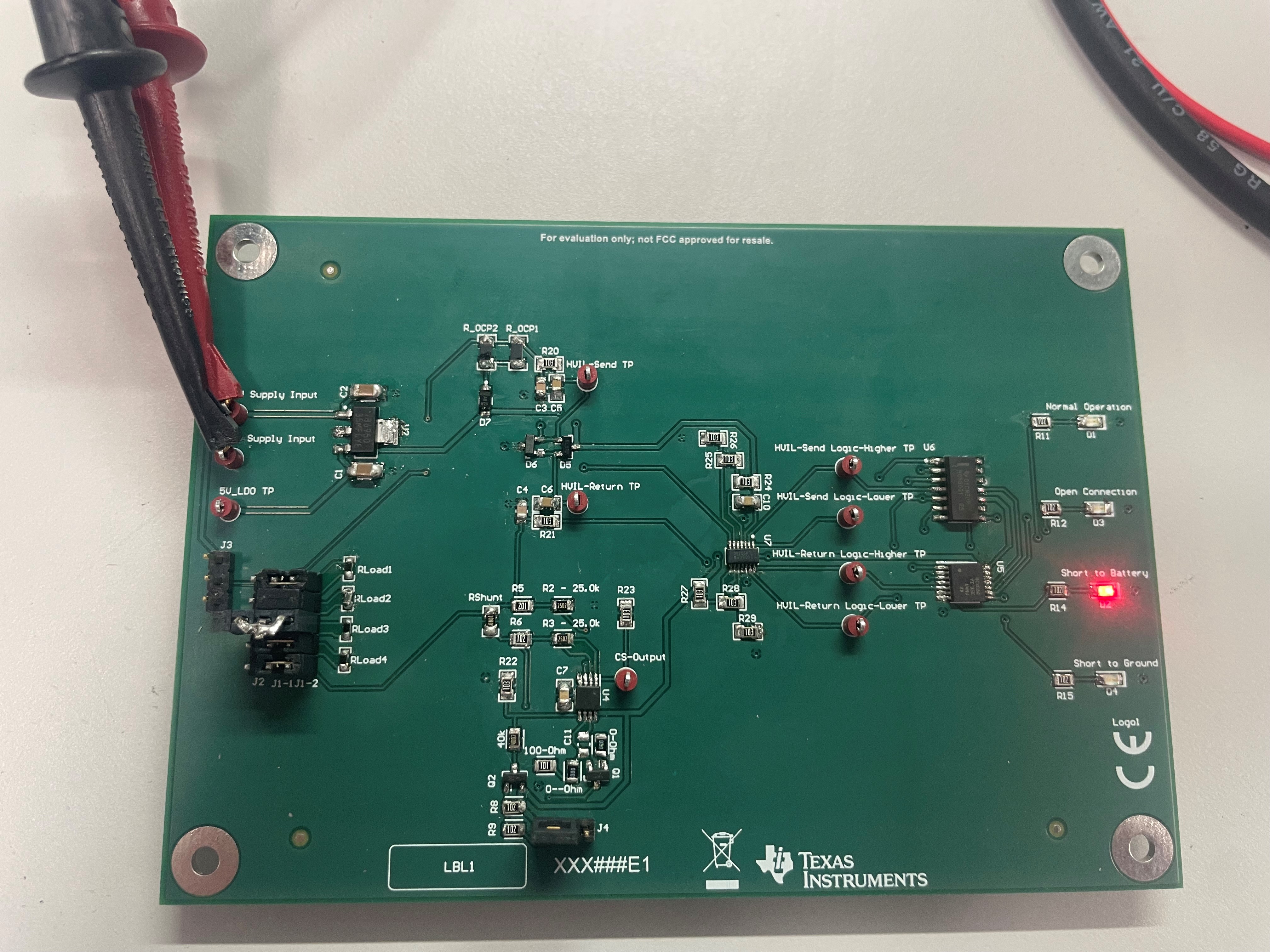

図 3-8 に、ディセーブル (シャットダウン) モードに構成された TIDA-020069 ボードを示します。この状態では、コネクタ J4 のディセーブル電圧は論理レベル High にプルされています。この信号がアクティブ High になると、アンプは無効化されます。定電流源の出力電流は 100 分の 1 に減少します。また、ディセーブル モードでは、HVIL 負荷の両端の電圧降下も 100 分の 1 に低減され、HVIL-Send と HVIL-Return の電圧範囲はバッテリ短絡障害モードと同じように見えます。この入力信号を使うと、全体システムが HVIL 読み取りを続ける準備が整うまで HVIL 設計を強制的に故障状態にする手動オーバーライドも可能です。

この状態に対応して、図 3-8 の「Short to Battery」(バッテリへの短絡) LED インジケータが点灯します。これにより、この状態での HVIL-Send および HVIL-Return 電圧の論理的解釈を確認できます。

図 3-11 ディセーブル (シャットダウン) のテスト結果

図 3-11 ディセーブル (シャットダウン) のテスト結果