JAJU948 September 2024

3.3 テスト結果

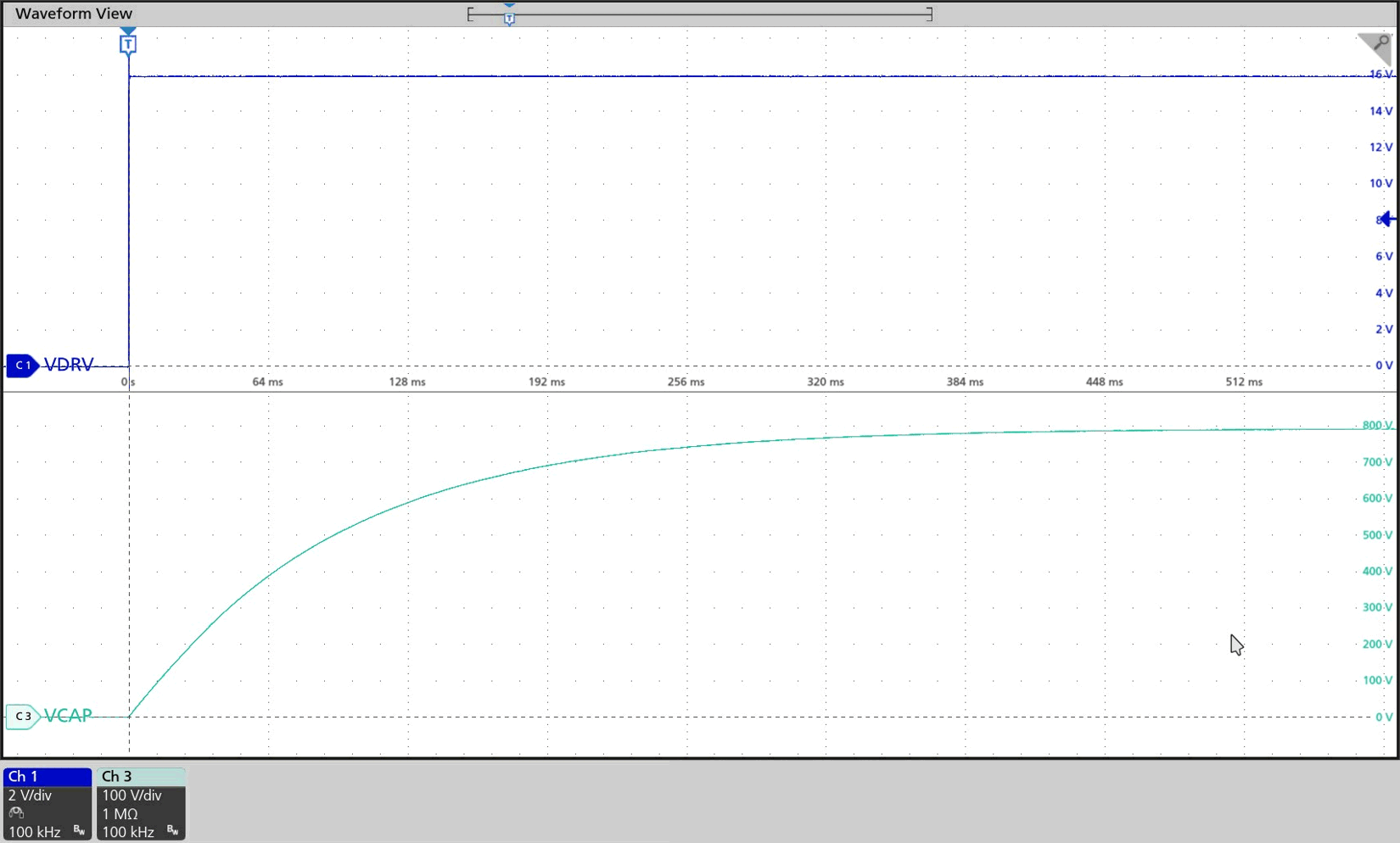

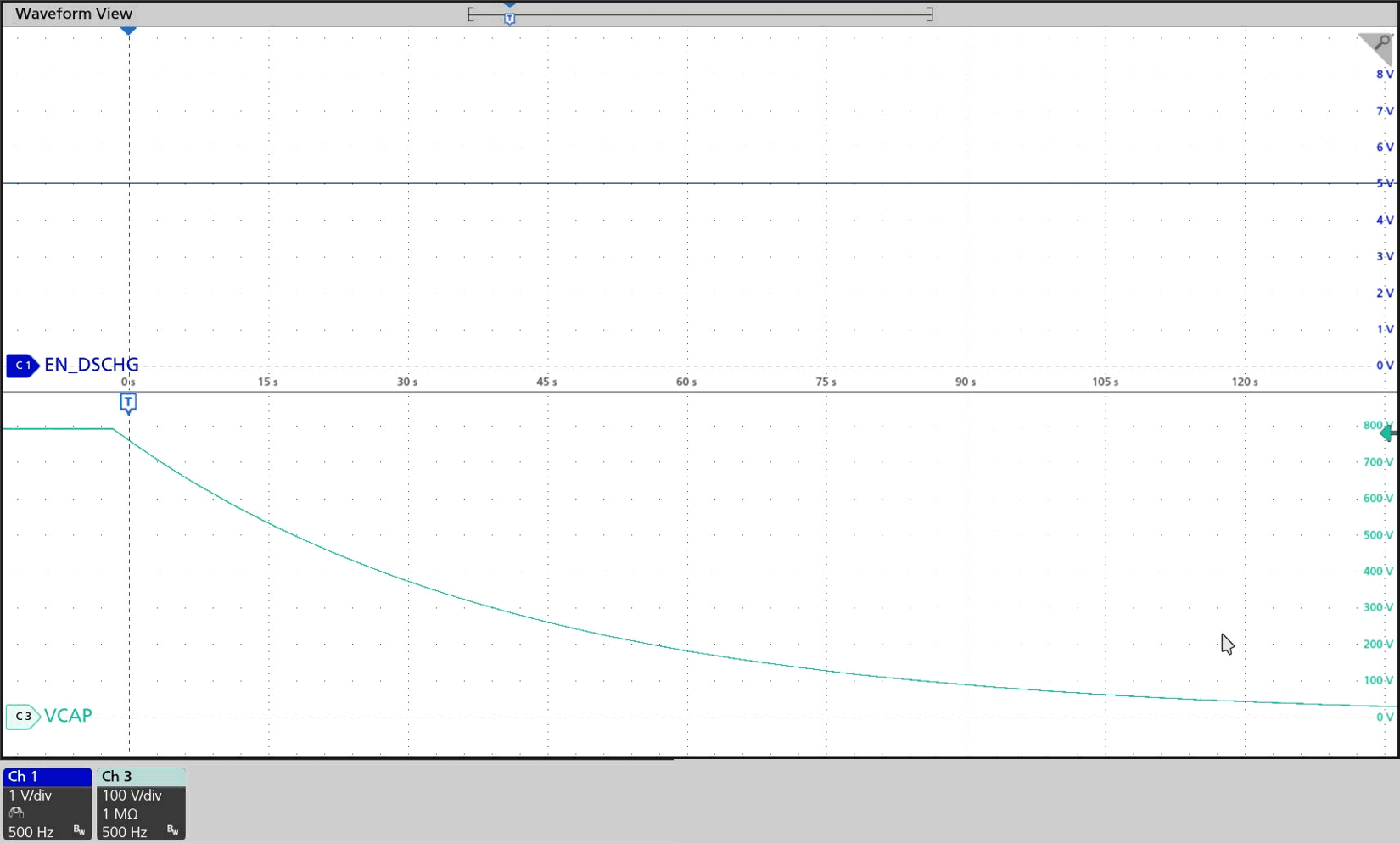

図 3-3 に代表的なプリチャージ サイクル、図 3-4 に放電サイクルを示します。

- VDRV は、TPSI3100-Q1 の 2 次側の駆動ピンです。

- VCAP は、コンデンサ バンクの両端の電圧です。

- EN_DSHCG は、TPSI2140-Q1 のイネーブル信号です。

図 3-3 プリチャージ サイクル

図 3-3 プリチャージ サイクル 図 3-4 放電サイクル

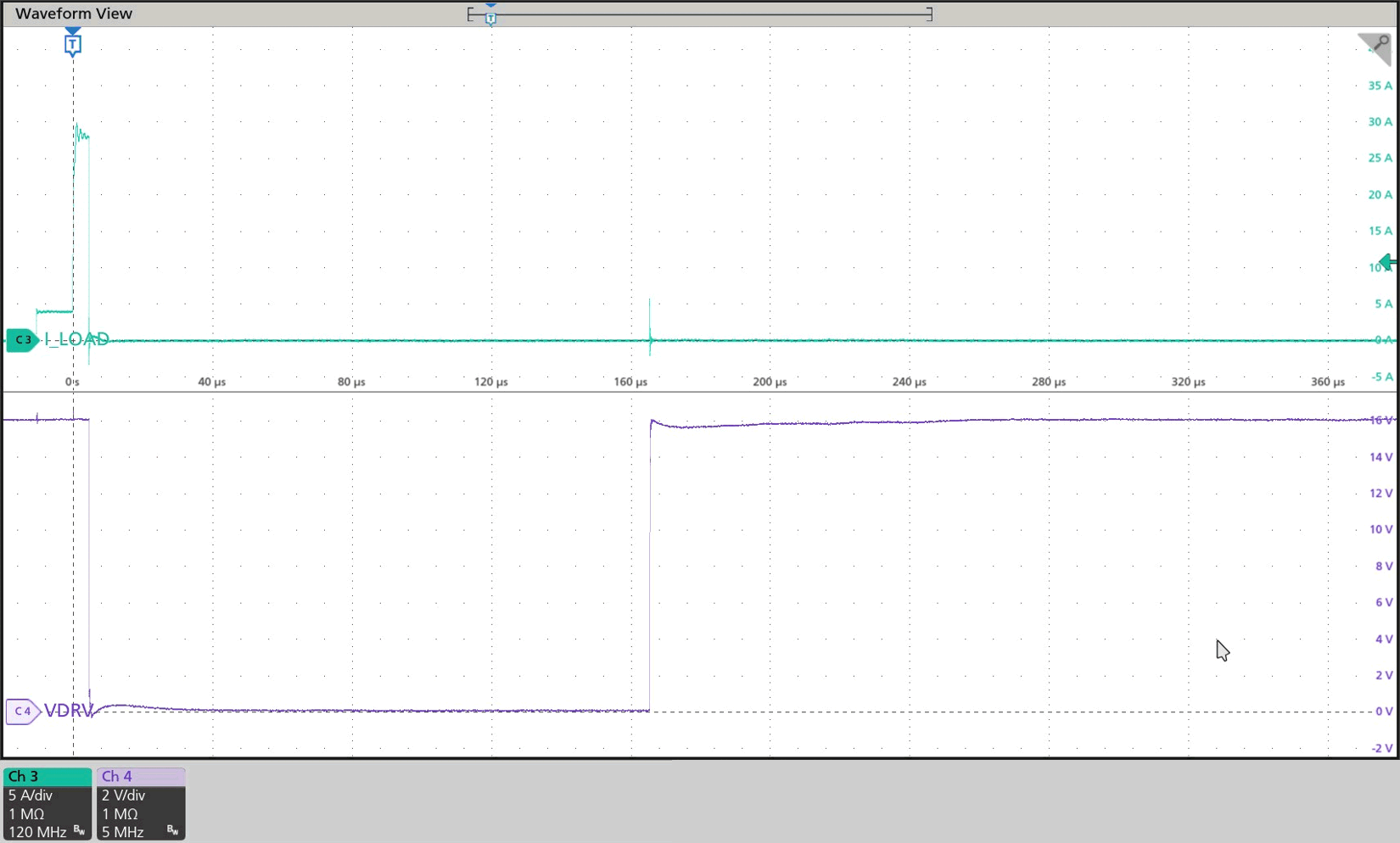

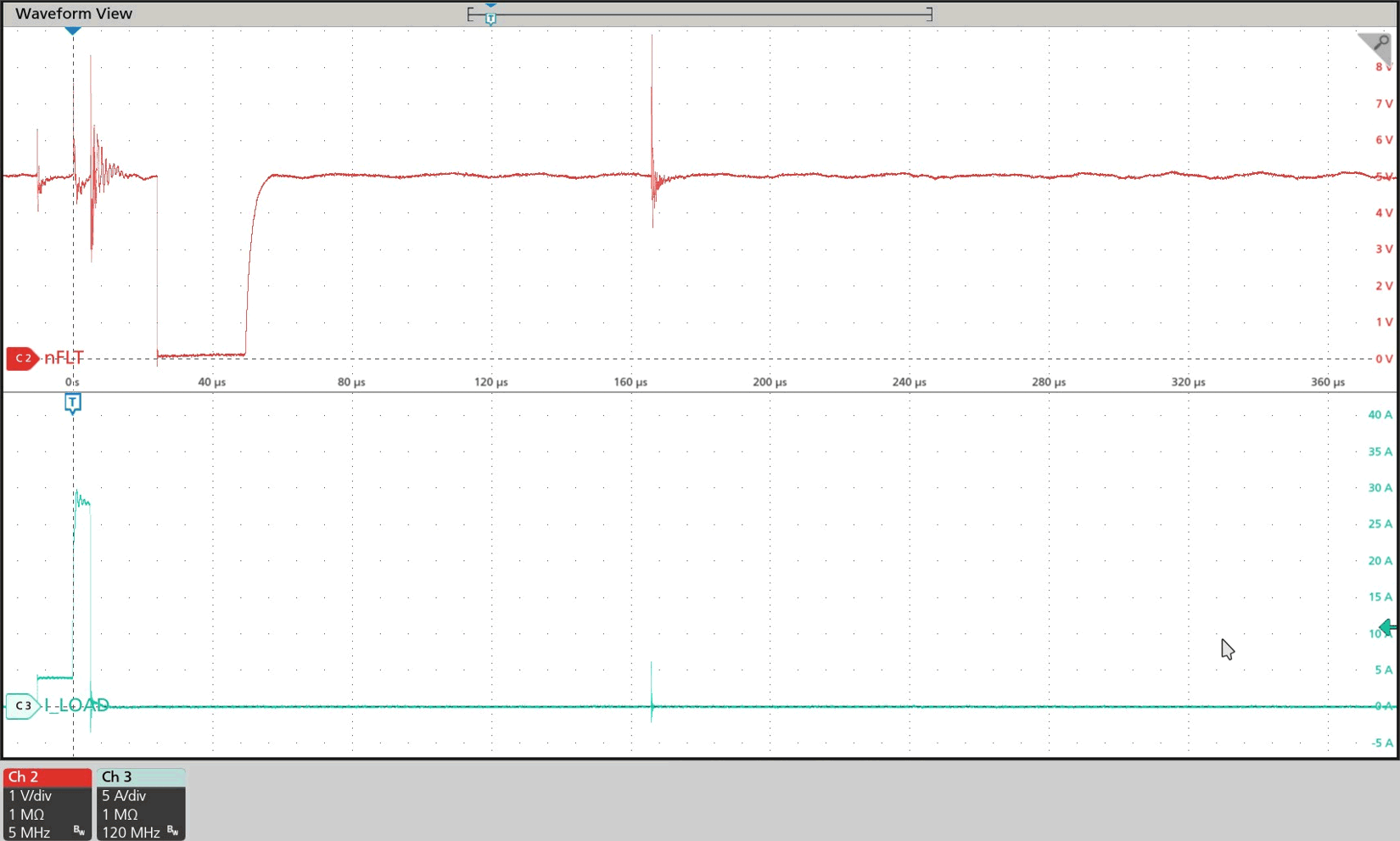

図 3-4 放電サイクル図 3-5 に、電流が 25A の制限を超えた後に VDRV ピンがディセーブルになるところを示します。自動復帰期間が経過すると、駆動ピンが再度アサートされます。同様に、図 3-6 では、30μs が経過した後に 1 次側の nFLT ピンがプルダウンされ、フォルトが通知されます。さらに 30μs が経過すると、このピンは再びプルアップされます。

図 3-5 VDRV のディセーブルおよび再イネーブル

図 3-5 VDRV のディセーブルおよび再イネーブル 図 3-6 1 次側フォルト通知

図 3-6 1 次側フォルト通知