JAJU957 November 2024

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1システムの説明

- 2システム概要

- 3システム設計理論

- 4リンク バジェット

- 5ハードウェア、ソフトウェア、テスト要件、テスト結果

- 6設計とドキュメントのサポート

- 7著者について

3.3 PCB

このリファレンス デザインでは、PCB に 4 層の積層を使用しています。積層は、アンテナの性能にとって非常に重要です。このセクションでは、既存の積層と、レイアウトに関連したコスト削減手法のいくつかを詳しく説明します。

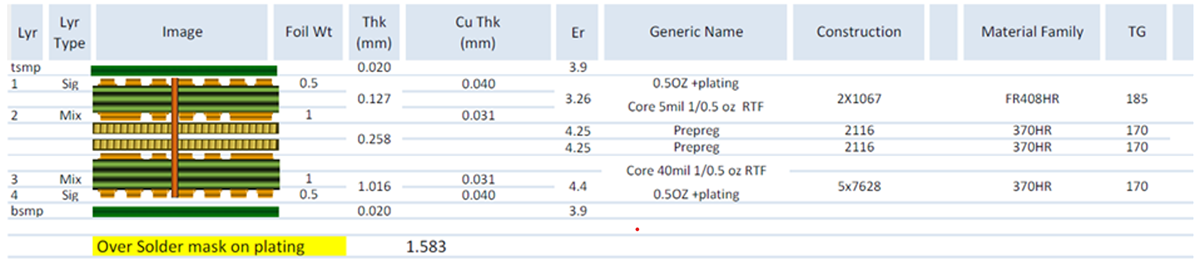

図 3-22 に、PCB 積層の詳細を示します。

図 3-22 PCB 積層

アンテナは PCB の最上層 (Lyr 1) に実装されています。この層には FR408HR 誘電体があります。誘電体の重要な特性をいくつか以下に示します。

- 誘電体は、2 x 1067 (2 層構造) のスプレッド ガラス構造を採用しています。この構造は、ガラス織り効果を低減し、損失を低減するのに役立ちます。

- 誘電体の厚さは 5mil (127um) です。この厚さの値は、インピーダンス マッチングに合わせて調整されます。

- 誘電体の Dk 値は 3.3 です。

- コア材料です。

注:

- 誘電体の厚さを変えると、インピーダンスのミスマッチが生じて放射電力の反射がより増える可能性があるため、誘電体の厚さは変えないでください。

- プリプレグ材はアンテナ層に使用しないでください。アンテナ以外の層には、プリプレグを使用できます。

接地された共平面導波管 (GCPW) 伝送ラインは、RF 信号をアンテナに伝送するために使用されています。以下に、アンテナ層とグランド層に関する重要な考慮事項を示します。

- アンテナ層の仕上がり銅箔の厚さは 40μm です。

- グランド プレーン (アンテナ プレーンの下、第 2 層) の厚さは 1oz (1oz が利用できない場合は 0.5oz も使用可能)。

- PCB 表面仕上げは OSP または浸漬銀です。注: ENIG 表面仕上げは、ミリ波周波数範囲で挿入損失が大きくなる可能性があるため推奨されません。

リファレンス デザインの PCB 全体の厚さは 1.6mm です。

注: テキサス・インスツルメンツの積層をそのまま使用することを推奨します。別の積層を希望する場合は、3D EM ソルバーが推奨され、アンテナの最適化を行う必要があります。

以下に、PCB 設計のコスト削減に効果があるとされる手法の一部を示します。