JAJU959 November 2024

- 1

- 概要

- リソース

- 特長

- アプリケーション

- 6

- 1システムの説明

- 2システム概要

- 3ハードウェア、ソフトウェア、テスト要件、テスト結果

- 4設計とドキュメントのサポート

- 5著者について

3.4.3.1 ラボ 2 のソフトウェア オプションの設定

- このラボを実行するには、前のセクション、図 3-9 で説明したようにハードウェアが設定されていることを確認します。

- セクション 3.2.1 の概要に従って CCS プロジェクトを開きます。powerSUITE を使用している場合は、手順 3 に進みます。それ以外の場合は手順 4 に進みます。

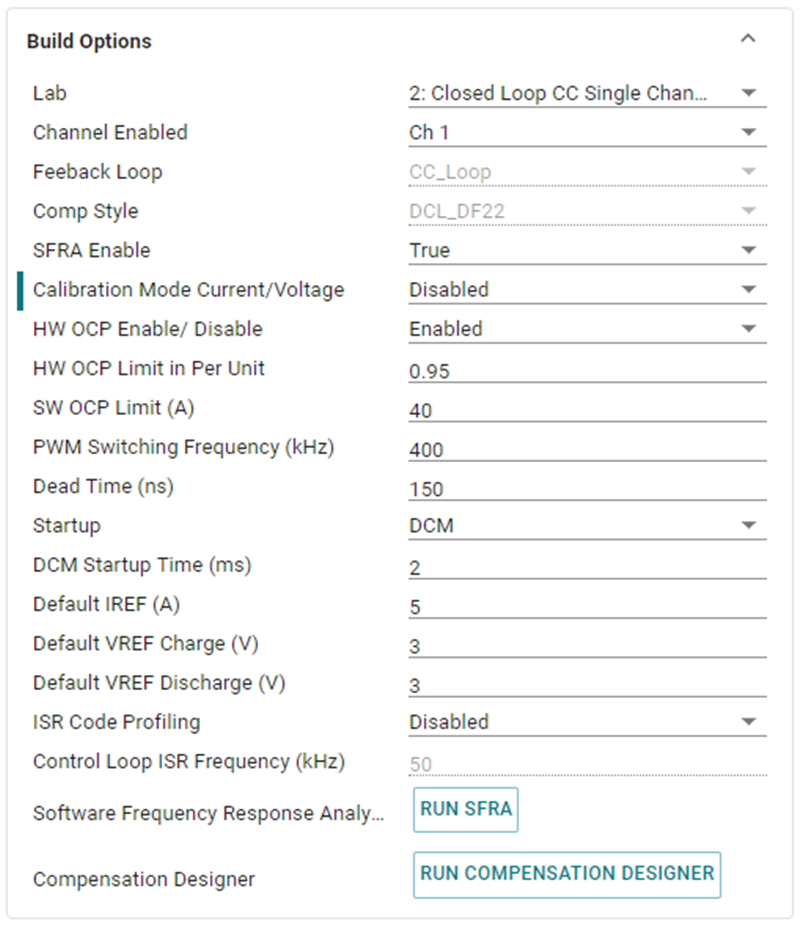

- SYSCONFIG ページを開き、[Build Options] セクションで以下を選択します。

- ラボは [Lab 2: Closed Loop CC Single Channel] を選択します。

- チャンネルを選択します。

- SFRA をイネーブルにします。

- [Run Compensation Design] ボタンをクリックして、Compensation Designer

を開きます。

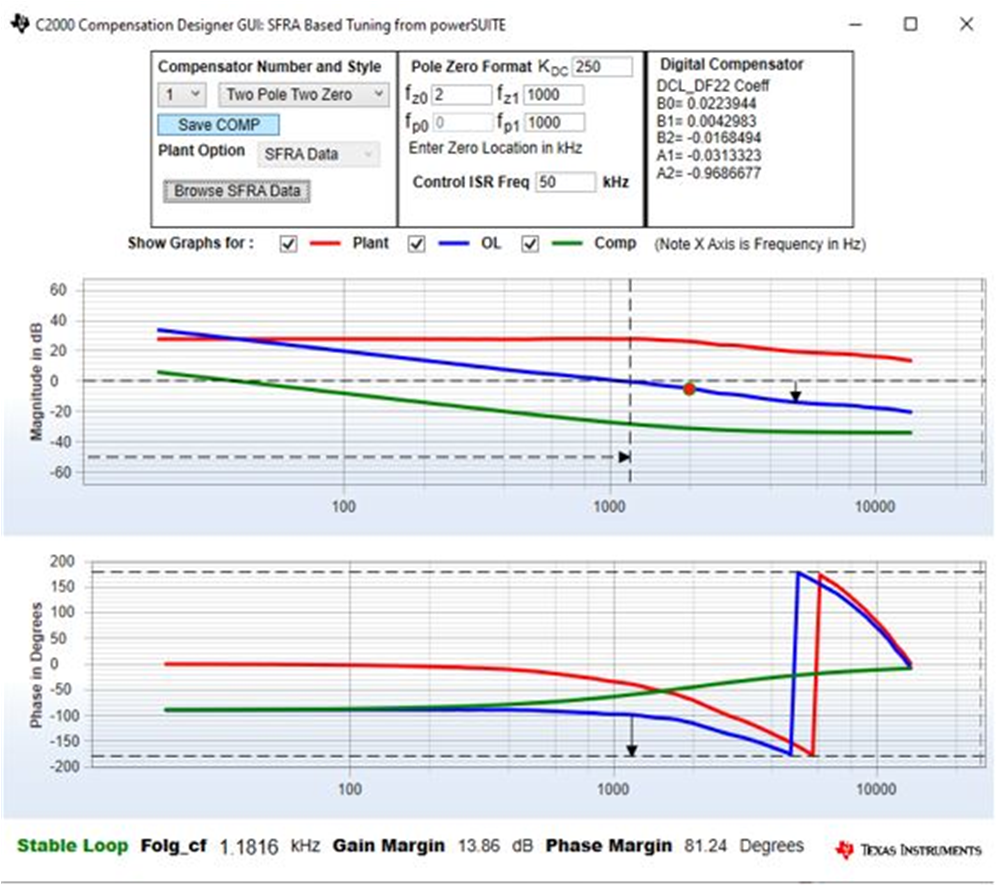

を開きます。 - 補償デザイナが起動し、有効な SFRA データ ファイルを選択するように求められます。ラボ 1 の実行から補償デザイナに SFRA データをインポートし、2 極、2 ゼロの補償器を設計します。この設計の繰り返し中により多くのマージンを確保して、ループが閉じたときにシステムが安定するようにします。

- 電流ループの補償パラメータを、図 3-18 に示します。

- [Save Comp] ボタンをクリックして、補償を保存します。 Compensation Designer ツールを閉じます。

- SYSCONFIG ページを保存します。

- powerSUITE 以外のバージョンのプロジェクトを使用する場合、[Build Settings] は solution_settings.h ファイルで直接変更されます。

C2000Ware_DigitalPower_Install_Location\powerSUITE\source\utilsに配置されています。#define LAB_NUMBER (2) #define CHANNEL_NUMBER (1) #define SFRA_ENABLED (true)

図 3-17 ラボ 2 のビルド オプション

図 3-17 ラボ 2 のビルド オプション 図 3-18 Compensation Designer を使用した電流ループのチューニング

図 3-18 Compensation Designer を使用した電流ループのチューニング