NEST041 February 2024 TMS320F280025C , TMS320F280039C , TMS320F280049C

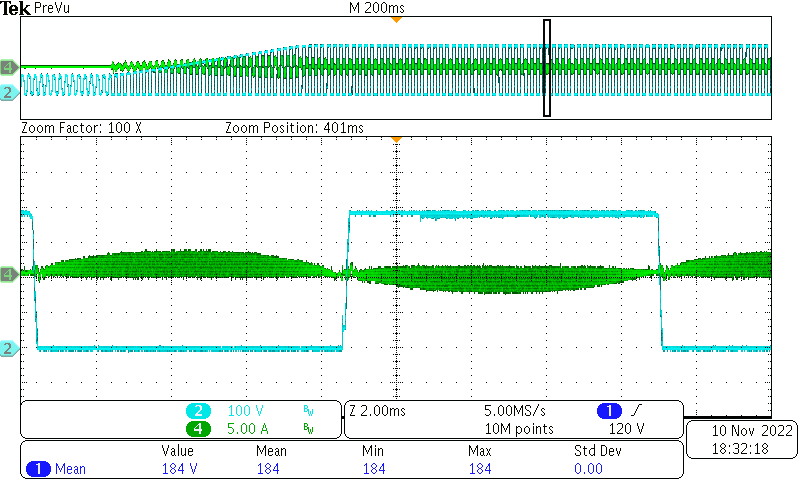

在設計升壓功率因數校正 (PFC) 等數位電源供應器時,您是否曾見過類似圖 1 中的電流振盪?

圖 1 在 PFC 級發生的電流振盪。來源:德州儀器

圖 1 在 PFC 級發生的電流振盪。來源:德州儀器您可能會認為這種不穩定的振盪是由於控制頻帶太快所造成,因此您會降低比例積分 (PI) 控制器的比例增益 (Kp) 和積分增益 (Ki),進而顯著降低交叉頻率。然後振盪就會消失。

但這是最好的解決方案嗎?低電流迴路頻寬會減慢控制速度,但您可能會發現總諧波失真 (THD) 測試失敗。而且有時當來源阻抗略大時,就會再次出現振盪。

這種不穩定性是否還有其他可能的原因?如何以足夠的相位裕度來實現最佳的控制頻寬?現在讓我們詳細分析數位控制迴路,以了解造成這種潛在錯誤的原因。我們也會向您說明如何檢查在控制韌體中是否發生這種不穩定性。

MCU 架構的數位控制

圖 2 以圖示顯示 MCU 架構的數位控制系統。

圖 2 數位控制系統是以微控制器為核心建置而成。來源:德州儀器

圖 2 數位控制系統是以微控制器為核心建置而成。來源:德州儀器控制迴路包含用於對目標電流/電壓進行取樣的類比數位轉換器 (ADC)、用於產生調整值的數位控制器,以及用於執行調整的脈衝寬度調變器 (PWM),可透過變更工作或頻率來變更目標電流/電壓。

切換模式電源供應器 (SMPS) 中的 ADC 取樣通常位於兩個切換週期的中點,這樣不僅可避免切換產生的雜訊干擾,也可取得連續傳導模式 (CCM) 中的功率電感器平均電流值。

數位控制器會在中斷服務例行程序 (ISR) 中加以計算,且可與 PWM 輸出同步觸發。觸發事件可能是以下其中一個事件:PWM 的「計數器」等於「零」、「週期」或特定值「CMP」。

雖然無法在控制器完成所有計算時立即更新 PWM,但隱藏暫存器必須在專用時刻載入 PWM 暫存器,例如當 PWM 計數器等於「零」或「週期」時。如果在計數器上升或下降時,PWM 值發生變化,很可能會產生錯誤的 PWM 操作,導致缺少脈衝或複製脈衝。

與類比控制系統不同,數位控制由取樣頻率執行,且取樣必須具有延遲時間 (Td) 以將新值重新載入 PWM。PWM 修改是透過調整翻轉時刻來實作,其在單緣調變時會發生一次 (向上計數/向下計數模式),且在雙緣調變時會發生兩次 (向上-向下計數模式)。因此,最小 Td 會是一個切換週期 Ts (如 圖 3a 所示),或是二分之一個切換週期 Ts/2 (如 圖 3b 所示),根據您選擇的調變重新載入頻率而定。

圖 3 PWM 調整帶來的最低延遲時間:(a) 向上模式,(b) 向上-向下模式。來源:德州儀器

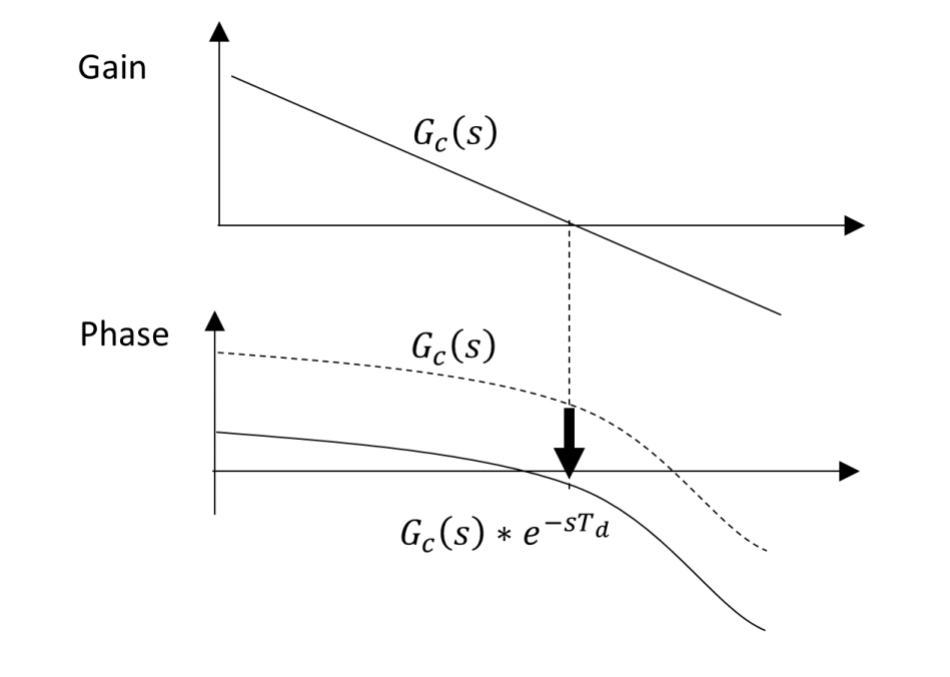

圖 3 PWM 調整帶來的最低延遲時間:(a) 向上模式,(b) 向上-向下模式。來源:德州儀器請檢視圖 4,Td 在其轉移函數中表示為 e-sxT d,這會減少相位裕度。當然,當相位裕度小於 45 度時,系統將變得不穩定,且會發生振盪。

圖 4 以波德圖顯示延遲時間的影響。來源:德州儀器

圖 4 以波德圖顯示延遲時間的影響。來源:德州儀器數位控制實作中的潛在程式碼錯誤

在正確執行的情況下,最小 Td 是一個切換週期 Ts、半個切換關週期 Ts/2。但如果您未考量 ADC、ISR 和 PWM 重新載入的後果,則將控制延遲延長至超過一個切換週期,可能會減少相位裕度並導致不穩定。

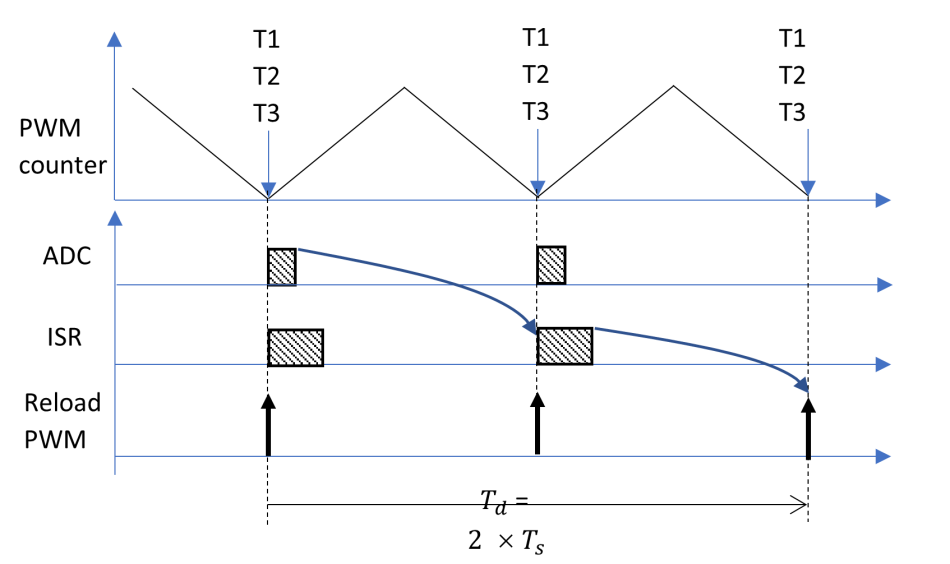

例如,在圖 5 中,ADC 的 ISR 觸發和 PWM 重新載入均在相同時刻開始,也就是當 PWM 計數器等於零的時候。

雖然所有區塊同時執行,但在這種情況下,是否可預期 Td 為零?當然不行!

圖 5 這是造成延遲時間增加的錯誤程式碼範例。來源:德州儀器

圖 5 這是造成延遲時間增加的錯誤程式碼範例。來源:德州儀器這是因為 ADC 轉換和 ISR 計算都需要多個 MCU 時脈週期;當 ISR 讀取 ADC 結果時,ADC 轉換仍未完成。因此,ISR 會取得「舊」取樣值來進行計算,而最新值的計算則會延遲至下一個切換週期。完成 ISR 計算後,新的 PWM 值只會寫入隱藏暫存器,並在下一個切換週期時重新載入。實際上,Td 的總控制延遲是兩個切換週期,即 2 x Ts。

除了此處所示的範例外,其他實作方式可能會造成類似的控制延遲延長,例如若您在 ISR 程式碼中,將讀取 ADC 值放在計算控制器後,或是在計算控制器前新增 N 週期演算法平均等。

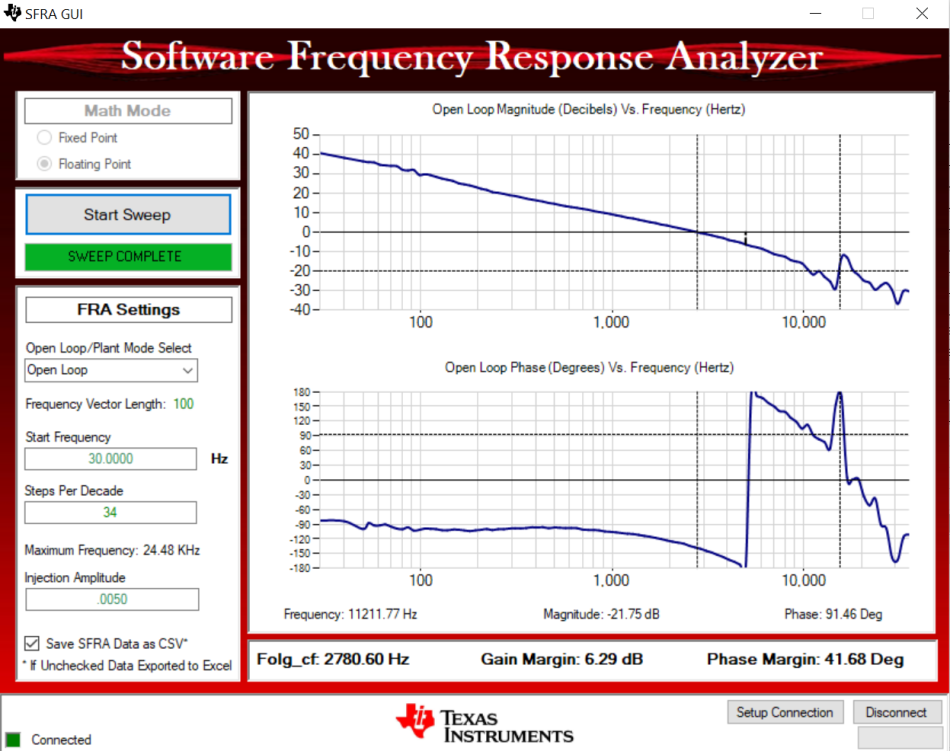

如圖 6 所示,若在發生圖 5 的錯誤實作時,將增益交叉頻率設定為約 3 kHz,則相位裕度為 41.68 度。這小於 45 度,且扼流圈電流具有顯著振盪 (如同圖 1 的波形),因此迫使您需將交叉頻率降至低於 2 kHz;隨後 iTHD 即會惡化,無法滿足要求。

圖 6 實作錯誤程式碼的波德圖。來源:德州儀器

圖 6 實作錯誤程式碼的波德圖。來源:德州儀器設計解決方案

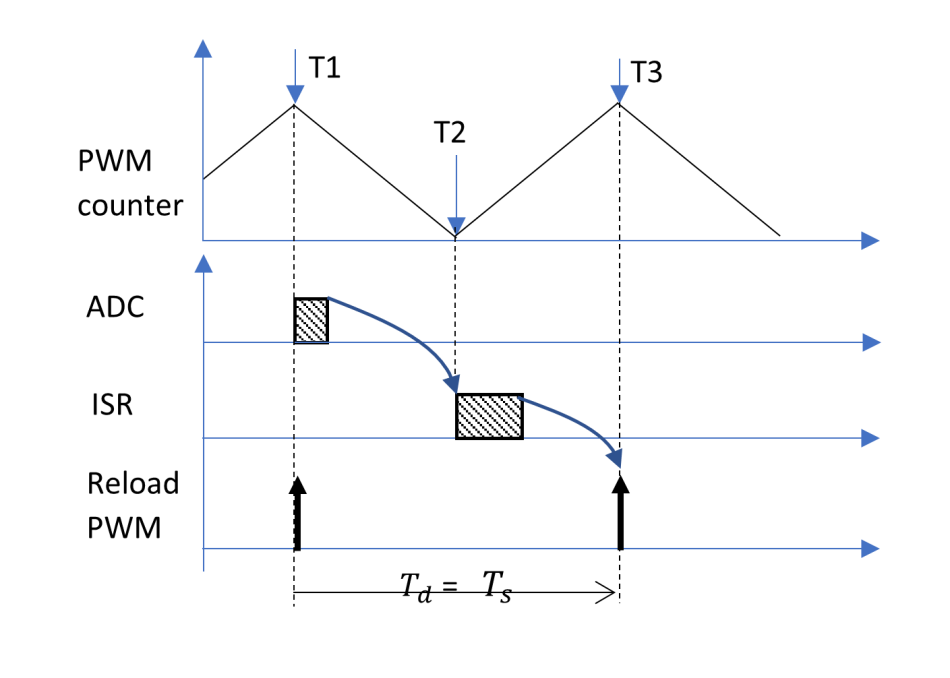

您可以透過將 ADC 轉換移至計數器 = 週期的時刻,並在下一個計數器 = 週期時進行重新載入 PWM 的作業,即可輕鬆解決此問題,如圖 7 所示。

圖 7 改善程式碼可減少控制延遲。來源:德州儀器

圖 7 改善程式碼可減少控制延遲。來源:德州儀器控制延遲會減少至一個切換週期。相位裕度會顯著增加,且電流振盪會消失,如圖 8 和圖 9 所示。

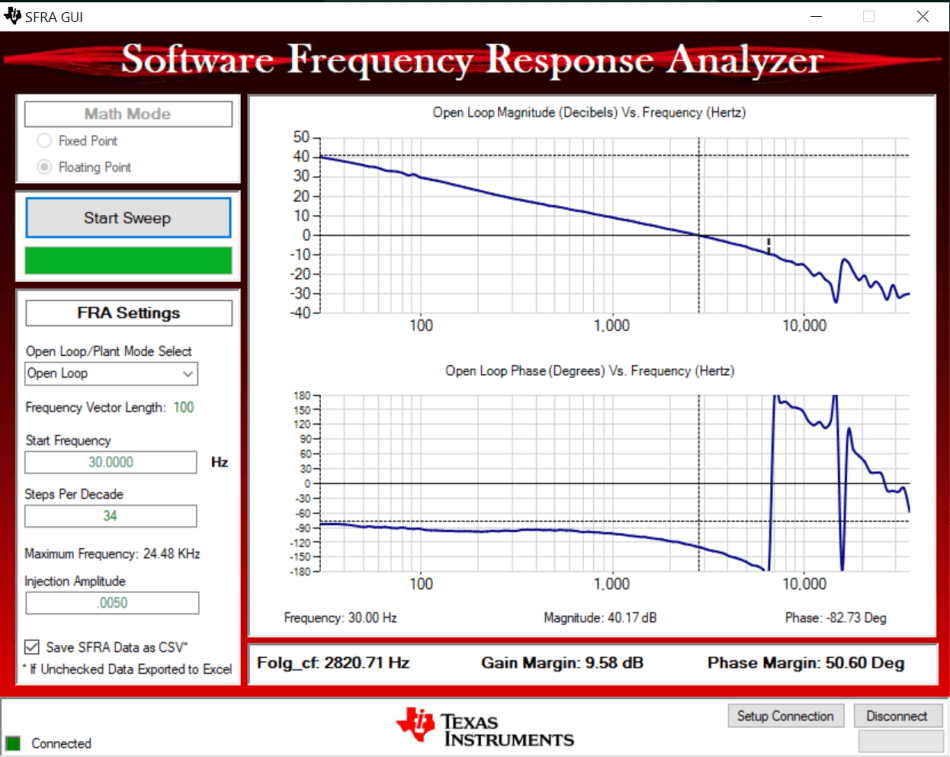

圖 8 程式碼經改善的波德圖。來源:德州儀器

圖 8 程式碼經改善的波德圖。來源:德州儀器 圖 9 程式碼經改善的波形。來源:德州儀器

圖 9 程式碼經改善的波形。來源:德州儀器組織良好的控制方案

在數位實作中從 ADC 取樣到 PWM 調整的控制延遲,將會減少相位裕度並造成振盪。解決此問題時,應考量 ADC 取樣、控制器計算和 PWM 重新載入的後果。組織良好的控制方案可將延遲最小化,達到二分之一個或一個切換週期,進而增加相位裕度與迴路頻寬。