SBAA497B May 2021 – April 2022 PCM3120-Q1 , PCM5120-Q1 , PCM6120-Q1 , TLV320ADC3120 , TLV320ADC5120 , TLV320ADC6120

- Trademarks

- 1Introduction

- 2Infinite Impulse Response Filters

-

3TLV320ADCx120 and PCMx120-Q1 Digital Biquad Filters

- 3.1 Filter Design Using PurePath Console

- 3.2 How to Generate N0, N1, N2, D1, and D2 Coefficients with a Digital Filter Design Package

- 3.3 Avoid Overflow Conditions

- 3.4 Digital Biquad Filter Allocation to Output Channel

- 3.5 Programmable Coefficient Registers for Digital Biquad Filters 1–6

- 3.6 Programmable Coefficient Registers for Digital Biquad Filters 7–12

- 4How to Program the Digital Biquad Filters on the TLV320ADCx120 and PCMx120-Q1

- 5Typical Audio Applications for Biquad Filtering

- 6Crossover Networks

- 7Voice Boost

- 8Bass Boost

- 9Removing 50 Hz–60 Hz Hum With Notch Filters

- A Digital Filter Design Techniques

- B Related Documentation

- B Revision History

3 TLV320ADCx120 and PCMx120-Q1 Digital Biquad Filters

The TLV320ADCx120 and PCMx120-Q1 devices support up to three programmable Digital Biquad Filters in the signal chain of each channel shown in Figure 1-1. The programmable Biquad Filters lie between the Digital Summer and the Digital Volume Control blocks. The Biquad Filters allow for custom low-pass, high-pass, or any other desired frequency shaping of the signal. By default, the frequency response for each Biquad Filter is an all-pass filter, meaning a frequency response with flat gain of 0 dB. A host can override the frequency response of these Biquad filters by changing the programmable coefficients of each Biquad Filter. To change the coefficients, the host must write the Biquad Filters coefficients before powering any ADC channels.

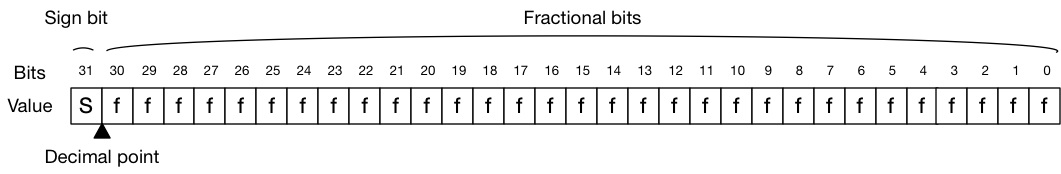

Equation 3 shows the quantized 32-bit transfer function implemented in the TLV320ADCx120 and PCMx120-Q1. The coefficients of these biquad filters [N0, N1, N2, D1, and D2] are each 32-bits wide, in 2s-complement format, and occupy four consecutive 8-bit registers in the TLV320ADCx120 and PCMx120-Q1 register space. With the Q-point in the 31st bit location (Q31), the filter coefficients are in 1.31 format with a range from –1 (0x80000000) to 0.9999999995 (0x7FFFFFFF). In this notation, the decimal point is assumed to be between bit 30 and bit 31. Bit 31 contains the sign bit, while bits 30–0 contain the fractional bits as shown in Figure 3-1. With this notation, all coefficients are normalized to less than 1. To convert a floating point number less than one to Q31 format, multiply the floating point number by 231 and truncate to the nearest integer. With this notation, the number 1, corresponding to a0 in the denominator, becomes 2–31 (0x7FFFFFF). Note that the coefficients N1 and D1 are multiplied by two. Thus, when using a digital filter design package to calculate these coefficients, divide by 2 the N1 and D1 before writing these coefficient registers. Also, note that coefficients D1 and D2 have a negative sign. So, multiply by –1 before writing D1 and D2 to the coefficient registers when using a digital filter design package.

Figure 3-1 Q-31 Format Representation

Figure 3-1 Q-31 Format Representation