SBAU361 December 2020 ADC3664

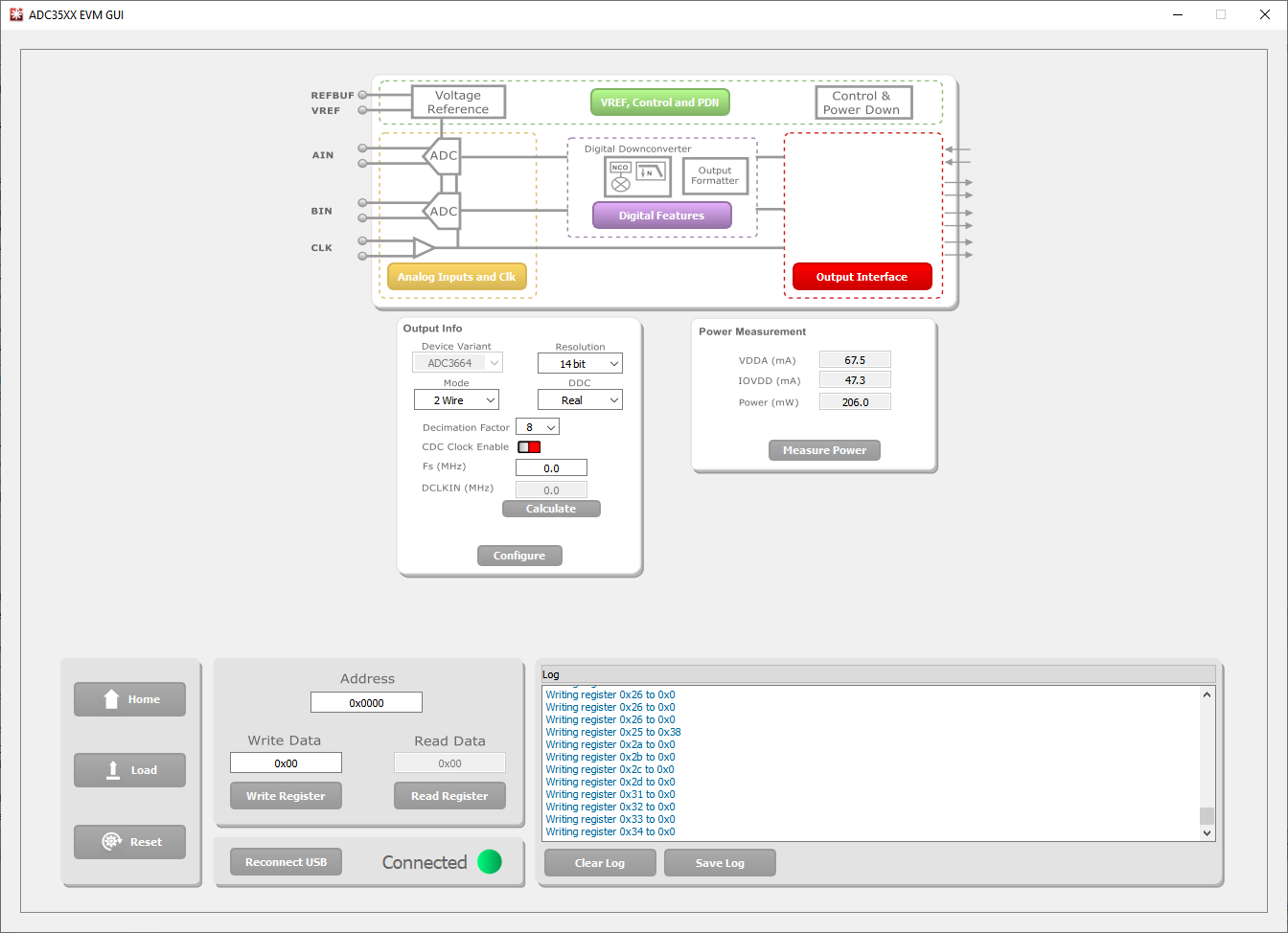

4.2.1 ADC35XX GUI: Real Decimation Mode Configuration

Table 4-2 14-Bit, Real Decimation, Sample

Rate and DCLKIN Examples

| Interface Mode | DCLKIN Multiplier (Serialization Factor) |

Example Sample Clock | Real Decimation Factor | Required DCLKIN Frequency |

|---|---|---|---|---|

| 2 Wire | 3.5 | 125 MSPS | 2 | 218.75 MHz |

| 1 Wire | 7 | 65 MSPS | 8 | 56.875 MHz |

| 1/2 Wire | 14 | 35 MSPS | 32 | 15.3125 MHz |

For this 14 bit, 2-Wire 8x Real Decimation example, apply a 125 MHz signal to J9 (sample clock) and a 54.6875 MHz signal to J7 (DCLKIN).

Attention: External ADC sampling

clock source and DCLKIN source must be frequency locked. If this is not performed, the

captured data will appear scrambled. If using the onboard clocking option, the sampling

clock and DCLKIN are frequency locked.

Apply a 5 MHz signal to J2 (ensure bandpass filter is used to reduce harmonics and noise of signal generator).

After launching the ADC35xx GUI perform the following steps:

- Under Resolution, select "14 bit".

- Under Mode, select "2 Wire".

- Under DDC, select "Real".

- For Decimation Factor, select "8".

- To calculate the DCLKIN frequency, enter "125" in the Fs(MHz) field, and click calculate. This is informational only.

- Ensure that "CDC Enable" is red (disabled).

- Click "Configure"

Figure 4-5 ADC35XXEVM GUI: ADC3664EVM 8x Real

Decimation

Figure 4-5 ADC35XXEVM GUI: ADC3664EVM 8x Real

Decimation