SBAU402 april 2023

6.1 EVM GUI Global Settings for ADC Control

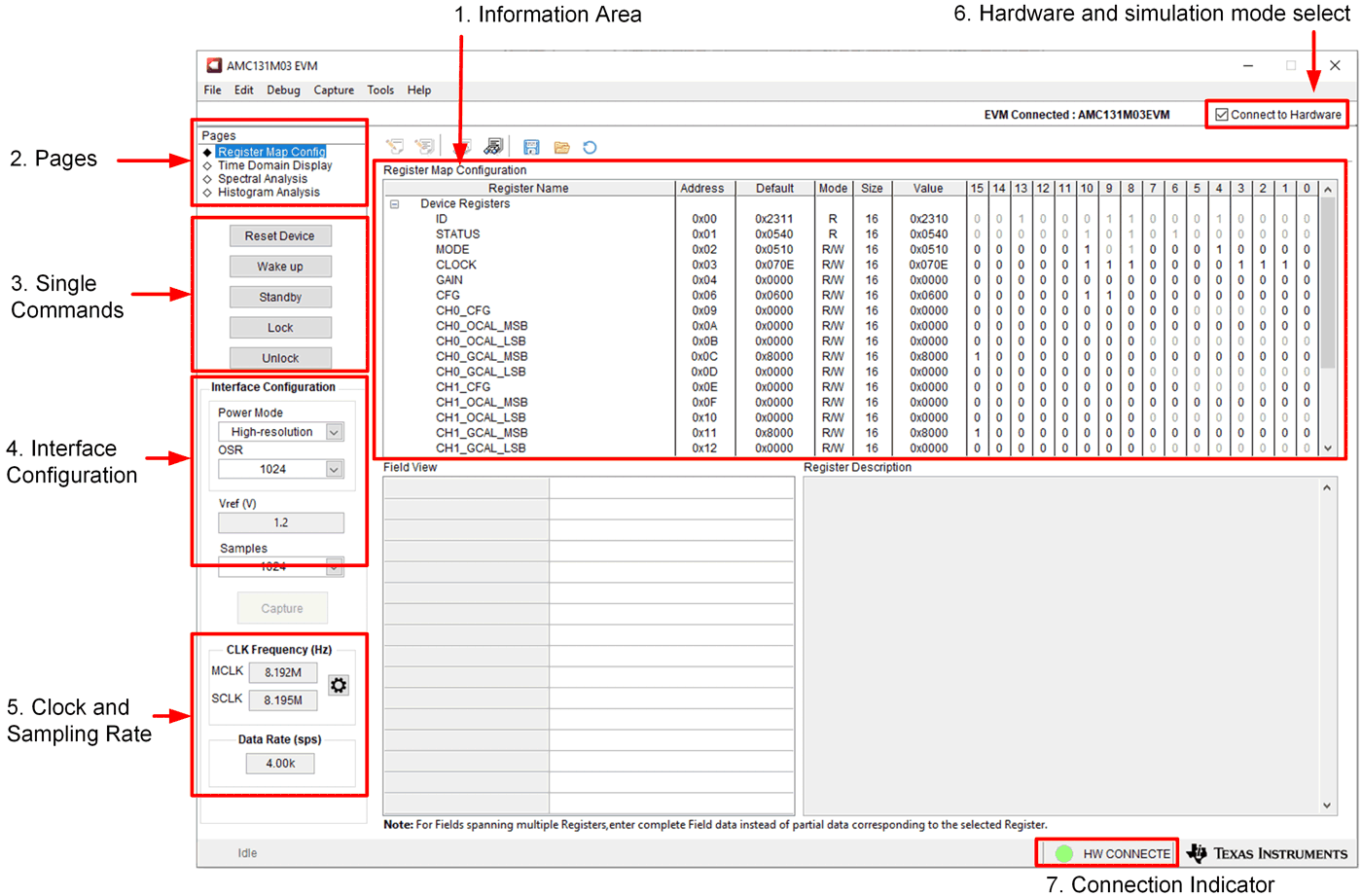

Although the EVM GUI does not allow direct access to the levels and timing configuration of the ADC digital interface, the EVM GUI does give users high-level control over virtually all functions of the AMC131M03 including interface modes, sampling rate, and number of samples to be captured. Figure 6-3 identifies the input parameters of the GUI (as well as their default values) through which the various functions of the AMC131M03 can be exercised.

Figure 6-3 EVM GUI Global Input Parameters

Figure 6-3 EVM GUI Global Input ParametersThere are four pages available in the AMC131M03EVM GUI. The information area displays the results of each of the pages. Each of these pages display a different control or measurement of the device. The Register Map Config page is used to read and write to the registers of the device. The Time Domain Display page is used to collect a set of data from the device and display the result. The Spectral Analysis page can determine the FFT of the collected data, and the Histogram Analysis page shows a histogram of the collected data and displays basic statistics of the result.

The Single Commands section allows for direct control of the device for five basic functions. First the Reset Device button sends a signal to the SYNC/RESET pin to reset the device. The Standby button puts the device into a low-power state in which all channels are disabled, and the reference and other non-essential circuitry are powered down. The Wake up button wakes the device from standby to convert mode. The Lock button lock the interface such that only the NULL, UNLOCK, and RREG commands are valid. The Unlock button unlocks the interface.

The Interface Configuration options in this pane allows the user to choose from different frame word sizes available on the AMC131M03. This section also sets the data rate by setting the oversampling ratio (OSR) in the ADC. Finally, this section can be used to set the power modes in the registers. The AMC131M03 can be set to high-resolution and low power modes in conjunction with the jumper settings of JP4 for the CLKIN pin, as outlined in Table 2-1. This information is also discussed in Section 2.2.

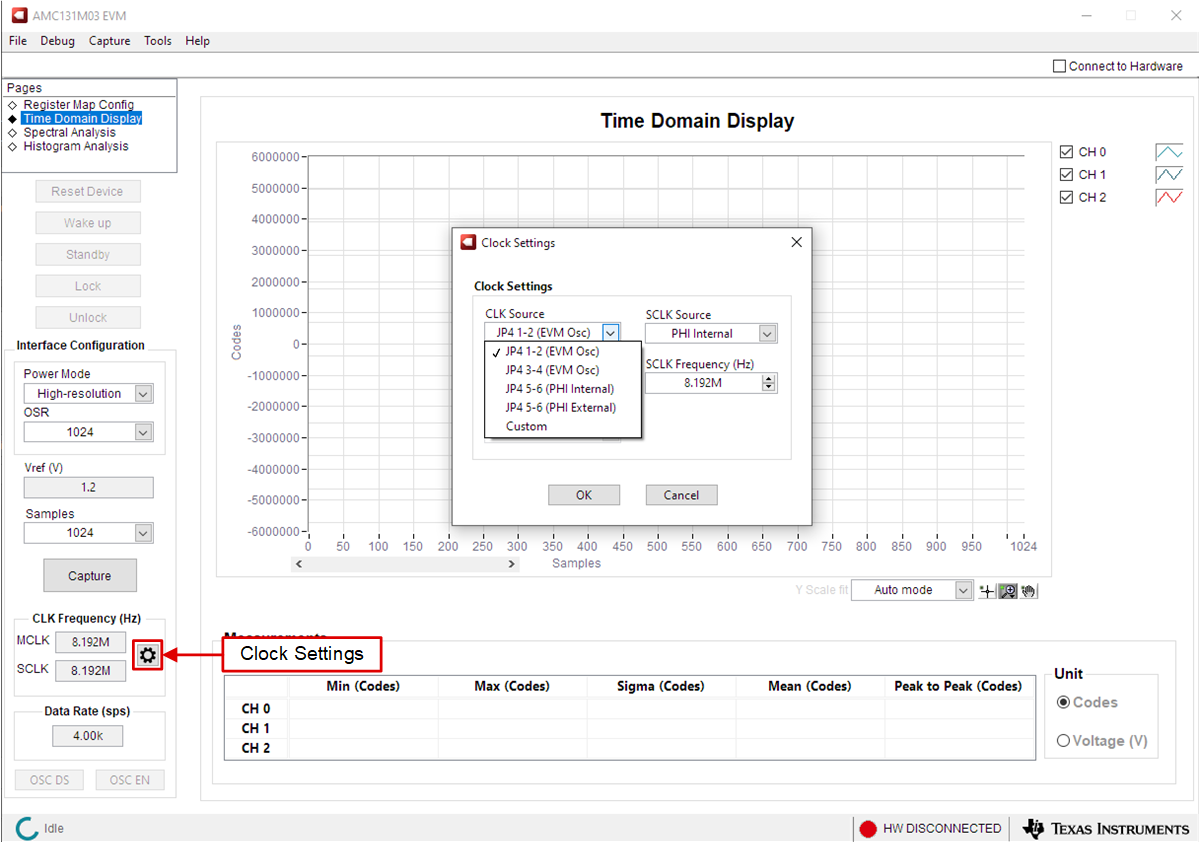

The Clock and Data Rate section allows the user to select the CLK source and SCLK source, and change the SCLK frequency (in Hz). These configurations can be implemented by checking the clock setting button in the CLK Frequency area and changing the dropdown as shown in Figure 6-4 . The clock source selection in the Clock Settings must match the jumper installed on JP4 on the AMC131M03EVM. Select Custom if an external CLKIN clock is provided directly to JP4[5].

Figure 6-4 Clock Setting Dialog

Figure 6-4 Clock Setting DialogThe GUI tries to match this frequency as closely as possible by changing the PHI PLL settings, but the achievable frequency can differ from the target value entered. This section also displays the data rate of the ADC as controlled by the OSR configuration.

The GUI is switched between hardware mode and simulation mode by checking and unchecking the Connected to Hardware box in the top right area of the screen at any time.