SBVU075 April 2022

2.4 Optional Load Transient Circuit Operation

The TPS7A57EVM-056 evaluation module contains an optional high-performance load transient circuit to allow efficient testing of the TPS7A57 LDO load transient performance. To use the optional load transient circuit, install the correct components in accordance with the application. Modify the input and output capacitance connected to the TPS7A57 LDO to match the expected operating conditions. As given by Equation 1, determine the desired peak current to test and modify the parallel resistor combination of R10, 11, R12, R13, and R14.

The slew rate of the load step can be adjusted by C11, R15, and R21. In this section, only R21 is adjusted to set the slew rate. For a 0-mA to 5-A load step, use Table 2-1 to help select a value of R21 that results within a desired rise or fall time.

| R21 | Rise Time | Fall Time |

|---|---|---|

| 49.9 kΩ | 11.5 µs | 31 µs |

| 30.9 kΩ | 7.4 µs | 19.7 µs |

| 24.9 kΩ | 6 µs | 15.1 µs |

| 21.5 kΩ | 3.9 µs | 14.8 µs |

| 4.12 kΩ | 980 ns | 2.5 µs |

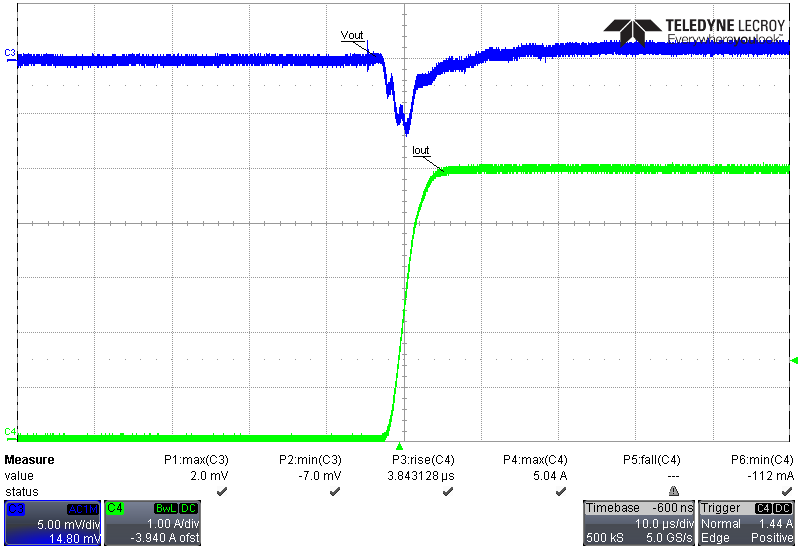

After the EVM is modified (if needed), and if the LMG1020 gate driver is used, connect a power supply to banana connectors J7(VCC) and J8 (GND) with a 5-V DC supply and a 1-A DC current limit. As illustrated in Figure 2-3, the TPS7A57 transient response is very fast and the output voltage recovers in well under 1 ms after the initial load transient. Therefore, use a load transient pulse duration limit of 1 ms to prevent excessive heating of the pulsed resistors (R10, R11, R12, R13, and R14). Configure a function generator for the 50-Ω output, in a 0-V DC to 5-V DC square pulse. If necessary, burst mode can be configured in the function generator for repetitive, low duty cycle, load transient testing.

Figure 2-3 provides example test data with R21 = 21.5 kΩ. The blue trace is the output voltage and the green trace is the output current. R10, R11, R12, R13, and R14 provide 5-A of pulsed load. The resulting test data shows a 0-mA to 5-A load step on VOUT of the LDO, with only a 22-μF capacitor on the output of the LDO.

The load transient circuit also provides footprints to install a damping network as needed. Install R23 and C15 to create a damping network if needed.

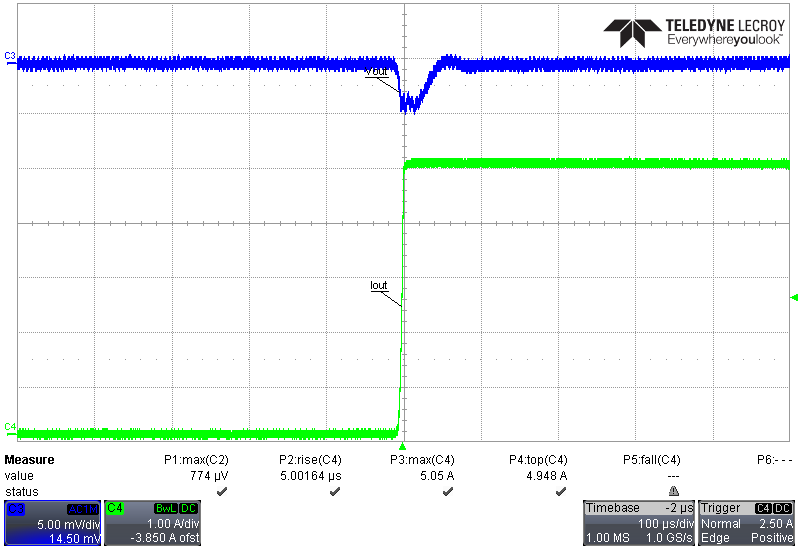

Alternatively, load transient measurements can be achieved by solely using the pre-installed Q1 load transient MOSFET. J15 can be used to provide a signal to Q1 using a function generator. Figure 2-4 depicts results using the MOSFET without the LMG1020 gate driver at a 5-A load.

Figure 2-3 TPS7A57EVM-056 Load Transient

Results

Figure 2-3 TPS7A57EVM-056 Load Transient

Results Figure 2-4 TPS7A57EVM-056 Load Transient

Results With a Q1 MOSFET

Figure 2-4 TPS7A57EVM-056 Load Transient

Results With a Q1 MOSFET